# **ISOW784x Quad-Channel Digital Isolator With Integrated DC-DC Converter Evaluation Module**

This user's guide describes the evaluation module (EVM) for the ISOW784x quad-channel digital isolators with integrated DC-DC converter. This EVM allows designers to evaluate device performance for fast development and analysis of isolated systems. The EVM supports evaluation of any of the TI triple- or quad-channel digital isolators in a 16DW or 16DWE package.

## **CAUTION**

This evaluation module is made available for isolator parameter performance evaluation only and is not intended for isolation voltage testing. To prevent damage to the EVM, any voltage applied as a supply or digital input/output must be maintained within the 0 V to 5.5 V recommended operating range.

## **Contents**

|   |                                                             |   |

|---|-------------------------------------------------------------|---|

| 1 | Introduction .....                                          | 2 |

| 2 | Overview .....                                              | 2 |

| 3 | Pin Configurations of ISOW784x Quad-Channel Isolators ..... | 2 |

| 4 | ISOW7841EVM Board Block Diagram and Image .....             | 3 |

| 5 | EVM Setup and Operation .....                               | 4 |

| 6 | Bill of Materials .....                                     | 5 |

| 7 | EVM Schematics and Layout .....                             | 5 |

## **List of Figures**

|   |                                                                 |   |

|---|-----------------------------------------------------------------|---|

| 1 | ISOW784x Quad-Channel Digital Isolator Pin Configurations ..... | 2 |

| 2 | ISOW7841EVM Configuration .....                                 | 3 |

| 3 | ISOW7841EVM Photograph .....                                    | 3 |

| 4 | Basic EVM Operation .....                                       | 4 |

| 5 | Typical Input and Output Waveforms .....                        | 4 |

| 6 | ISOW7841EVM Efficiency vs Load Current ( $I_{L_{SO}}$ ) .....   | 4 |

| 7 | ISOW7841EVM Schematic .....                                     | 5 |

| 8 | ISOW7841EVM PCB Layout .....                                    | 6 |

## **List of Tables**

|   |                         |   |

|---|-------------------------|---|

| 1 | Bill of Materials ..... | 5 |

|---|-------------------------|---|

## **Trademarks**

All trademarks are the property of their respective owners.

## 1 Introduction

This user's guide describes EVM operation with respect to the ISOW784x quad-channel digital isolators. However, the EVM may be reconfigured for evaluation of any of TI's triple- or quad-channel digital isolators in a 16DW or 16DWE package. This guide also describes the available channel configurations within the ISOW784x family, the EVM schematic, and typical laboratory setup. An efficiency plot and typical input and output waveforms are also provided.

## 2 Overview

The ISOW784x is a family of high-performance, quad-channel reinforced digital isolators with an integrated high-efficiency power converter. The integrated DC-DC converter provides up to 650 mW of isolated power at high efficiency and can be configured for various input and output voltage configurations. Therefore these devices eliminate the need for a separate isolated power supply in space-constrained isolated designs. The ISOW784x family of devices provide high electromagnetic immunity and low emissions while isolating CMOS or LVCMS digital I/Os. The signal-isolation channel has a logic input and output buffer separated by a silicon dioxide ( $\text{SiO}_2$ ) insulation barrier, whereas, power isolation uses on-chip transformers separated by thin film polymer as insulating material. Various configurations of forward and reverse channels are available. If the input signal is lost, the default output is high for the ISOW784x devices and low for the devices with the F suffix. These devices help prevent noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. Through innovative chip design and layout techniques, electromagnetic compatibility of the ISOW784x family of devices has been significantly enhanced to ease system-level ESD, EFT, surge and emissions compliance. The high-efficiency of the power converter allows operation at a higher ambient temperature.

## 3 Pin Configurations of ISOW784x Quad-Channel Isolators

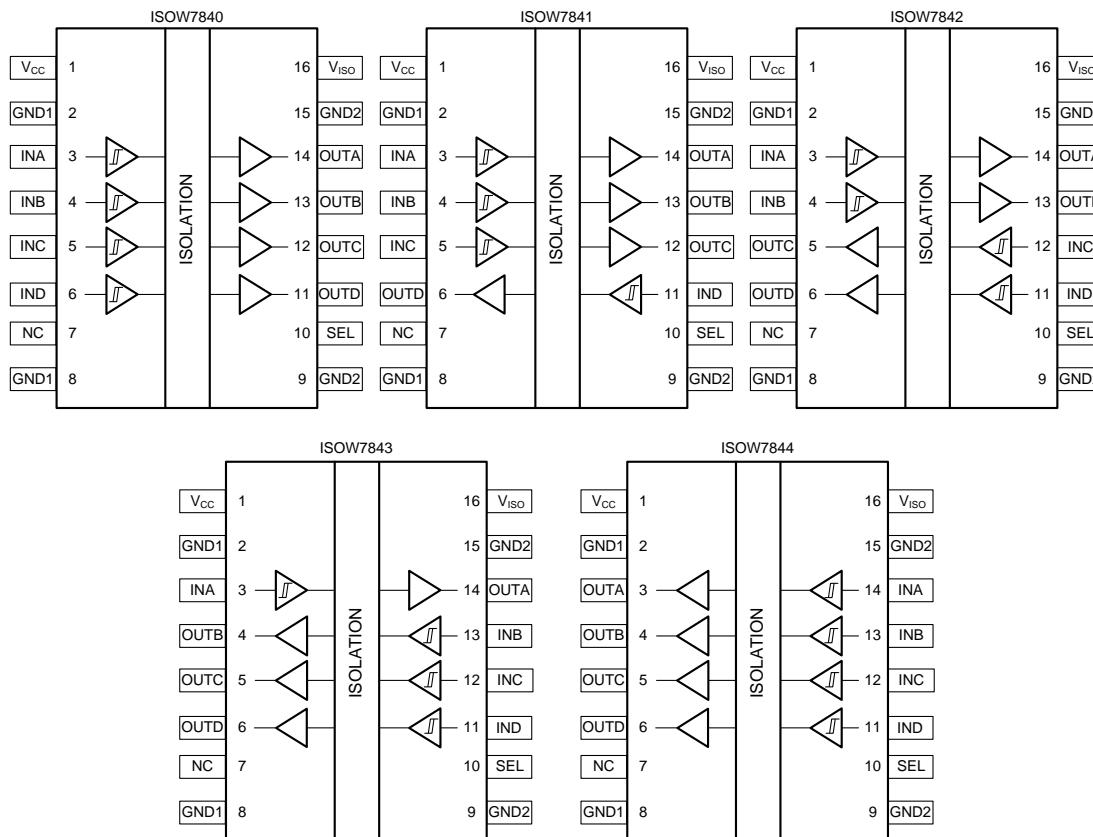

Figure 1 shows the ISOW784x quad-channel digital isolator pin configurations.

Figure 1. ISOW784x Quad-Channel Digital Isolator Pin Configurations

## 4 ISO7841EVM Board Block Diagram and Image

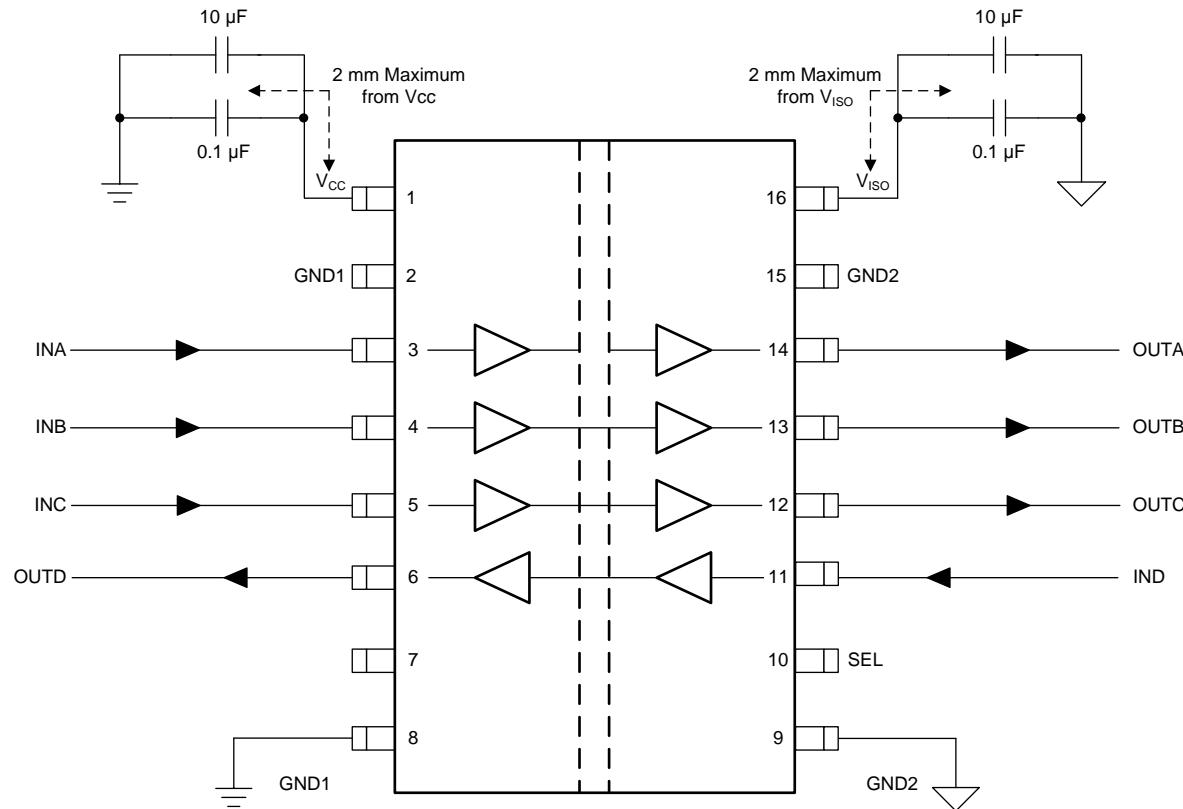

Figure 2 shows the board configuration for evaluation of the ISO7841 quad-channel isolator.

**Figure 2. ISO7841EVM Configuration**

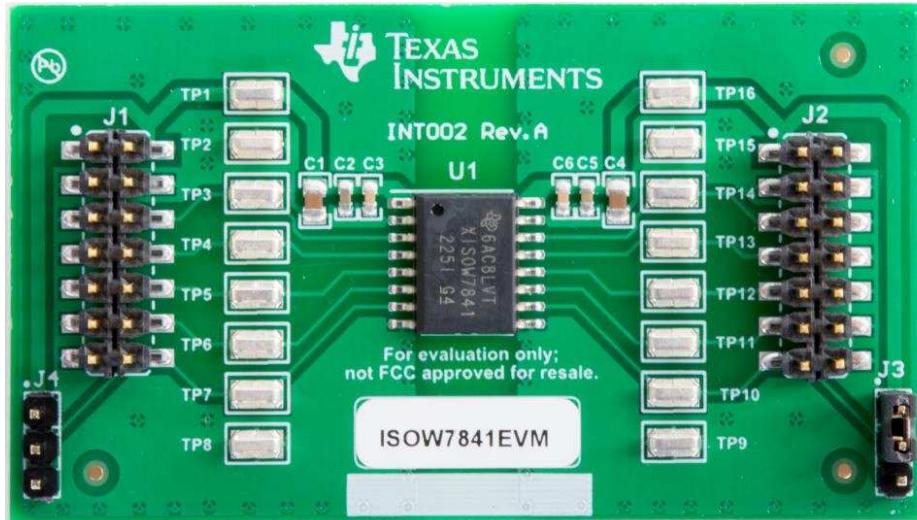

Figure 3 shows the photograph of the EVM.

**Figure 3. ISO7841EVM Photograph**

## 5 EVM Setup and Operation

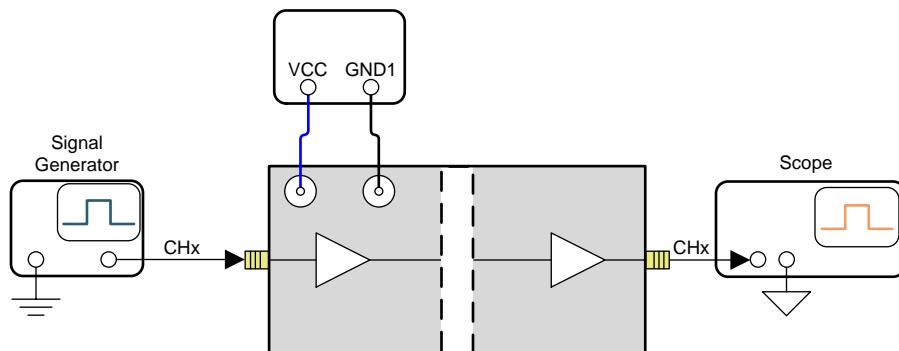

This section describes the setup and operation of the EVM for parameter performance evaluation. [Figure 4](#) shows the configuration for operating the ISOW784x quad-channel isolator EVM using an integrated DC-DC converter to generate output power supply.

**Figure 4. Basic EVM Operation**

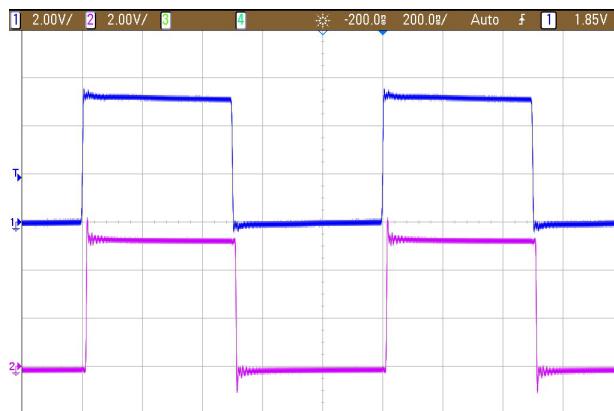

[Figure 5](#) shows typical input and output waveforms of the EVM for a 1-MHz clock. The input is shown as channel 1, and the output is shown as channel 2.

**Figure 5. Typical Input and Output Waveforms**

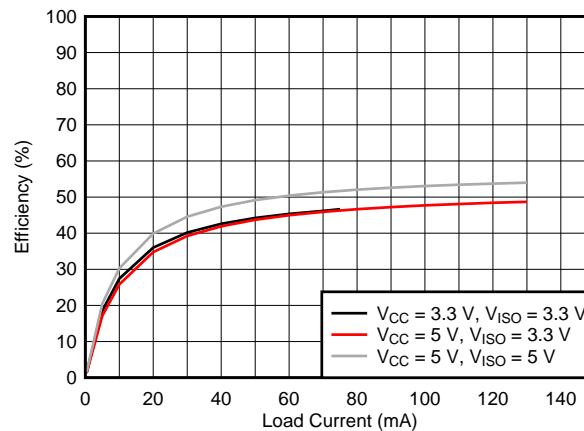

[Figure 6](#) shows typical efficiency vs load current plot of ISOW7841EVM for 3.3-V and 5-V output voltage configurations with input at 3.3-V and 5-V input voltages.

**Figure 6. ISOW7841EVM Efficiency vs Load Current ( $I_{iso}$ )**

## 6 Bill of Materials

[Table 1](#) shows the bill of materials (BOM) for this EVM.

**Table 1. Bill of Materials**

| Item | Designator                                                                            | Description                                         | Manufacturer      | Part Number        | Quantity |

|------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|--------------------|----------|

| 1    | C1, C4                                                                                | CAP, CERM, 10 $\mu$ F, 35 V, $\pm 10\%$ , X5R, 0805 | MuRata            | GRM21BR6YA106KE43L | 2        |

| 2    | C2, C5                                                                                | CAP, CERM, 1 $\mu$ F, 50 V, $\pm 10\%$ , X5R, 0603  | MuRata            | GRM188R61H105KAALD | 2        |

| 3    | C3, C6                                                                                | CAP, CERM, 0.1 $\mu$ F, 25 V, $\pm 5\%$ , X7R, 0603 | AVX               | 06033C104JAT2A     | 2        |

| 4    | H1, H2, H3, H4                                                                        | Bumper, Hemisphere, 0.44 X 0.20, Clear              | 3M                | SJ-5303 (CLEAR)    | 4        |

| 5    | J1, J2                                                                                | Header, 100mil, 7x2, SMT                            | Molex             | 0015912140         | 2        |

| 6    | J3, J4                                                                                | Header, 100mil, 3x1, Gold, TH                       | Samtec            | HTSW-103-07-G-S    | 2        |

| 7    | SH-J1                                                                                 | Shunt, 100mil, Gold plated, Black                   | Samtec            | SNT-100-BK-G       | 1        |

| 8    | TP1, TP2, TP3, TP4, TP5, TP6, TP7, TP8, TP9, TP10, TP11, TP12, TP13, TP14, TP15, TP16 | Test Point, Miniature, SMT                          | Keystone          | 5019               | 16       |

| 9    | U1                                                                                    | ISO7841DWE                                          | Texas Instruments | ISO7841DWER        | 1        |

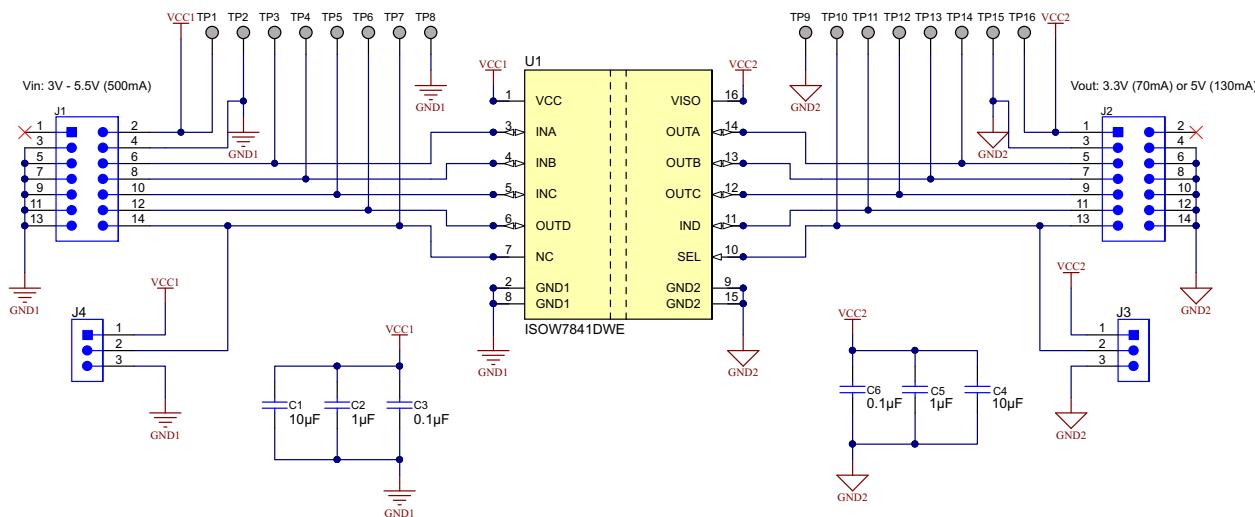

## 7 EVM Schematics and Layout

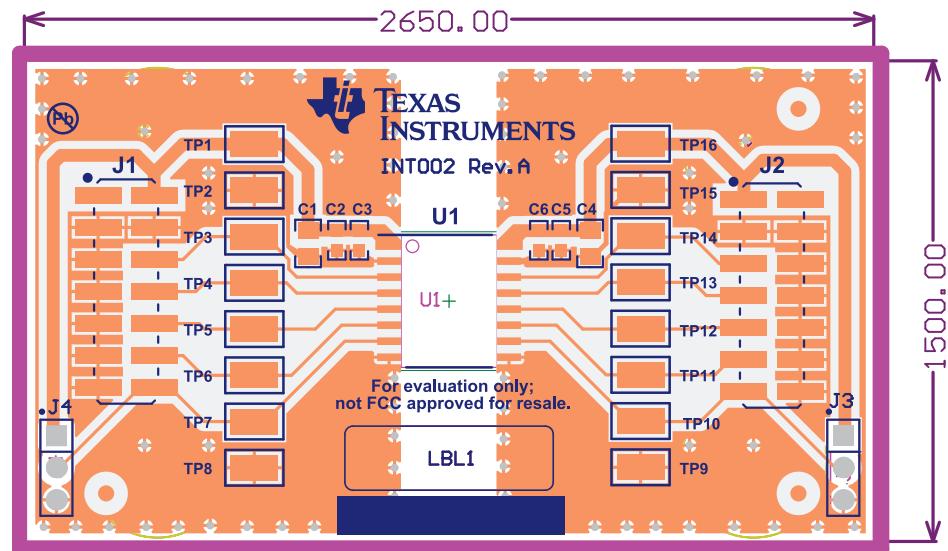

The ISO7841EVM is designed to accommodate any of the ISO784x quad-channel devices in a 16-pin DWE package. To evaluate any of the ISO784x quad-channel devices in a 16-pin DWE package, replace ISO7841DW with the device of interest on the ISO7841EVM PCB. No other component requires any modification. [Figure 7](#) shows the ISO784x EVM schematic and [Figure 8](#) shows the printed-circuit board (PCB) layout.

Copyright © 2017, Texas Instruments Incorporated

**Figure 7. ISO7841EVM Schematic**

Figure 8. ISOW7841EVM PCB Layout

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products (<http://www.ti.com/sc/docs/stdterms.htm>), evaluation modules, and samples (<http://www.ti.com/sc/docs/samptersms.htm>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2017, Texas Instruments Incorporated