## MAX98358

## PDM Input Class D Audio Power Amplifier

### General Description

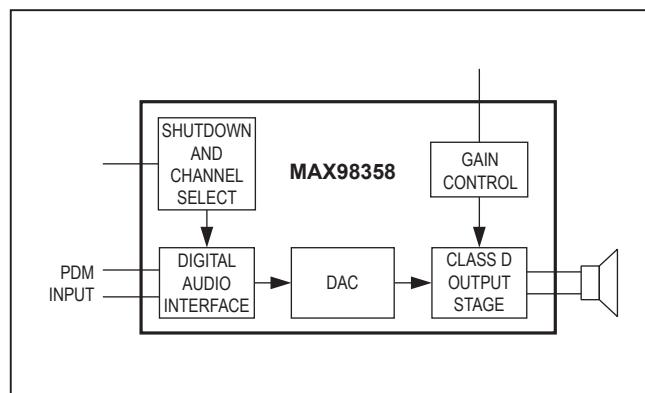

The MAX98358 is a digital pulse-density modulated (PDM) input Class D power amplifier that provides Class AB audio performance with Class D efficiency. This IC offers five selectable gain settings (3dB, 6dB, 9dB, 12dB, and 15dB) set by a single gain-select input (GAIN). The IC can be configured to produce a left channel, right channel, or (left/2 + right/2) output from the stereo input data.

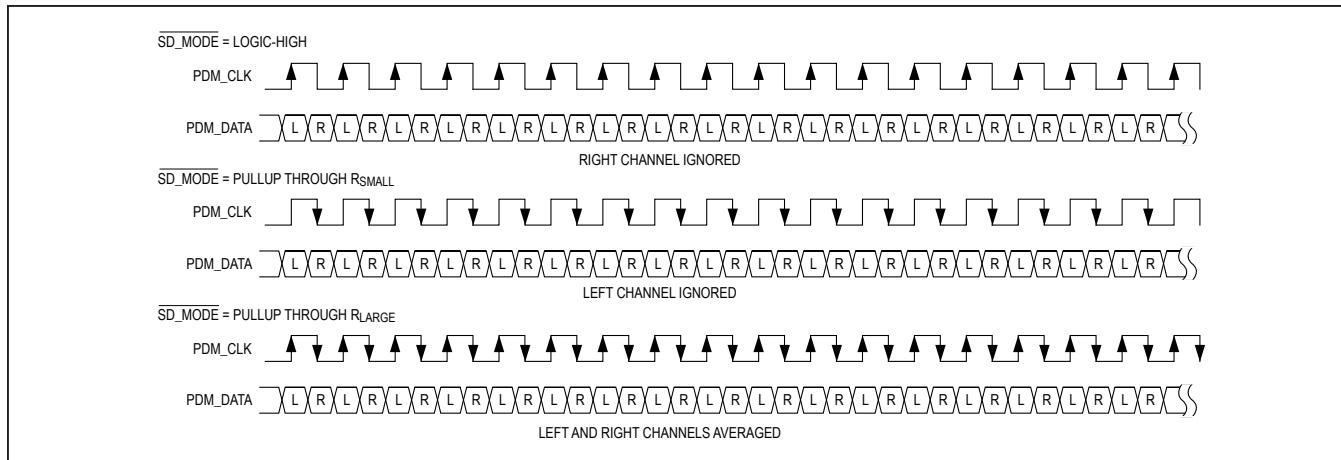

The MAX98358 takes a stereo pulse density modulated (SPDM) input signal directly into the DAC. Data on the rising edge of PDM\_CLK is considered left-channel data while data on the falling PDM\_CLK edge is right channel. A mono sum feature is also implemented with SPDM data input by summing the data from both rising and falling clock edges.

Active emissions-limiting, edge-rate limiting, and overshoot control circuitry greatly reduce EMI. A filterless spread-spectrum modulation scheme eliminates the need for output filtering found in traditional Class D devices and reduces the component count of the solution.

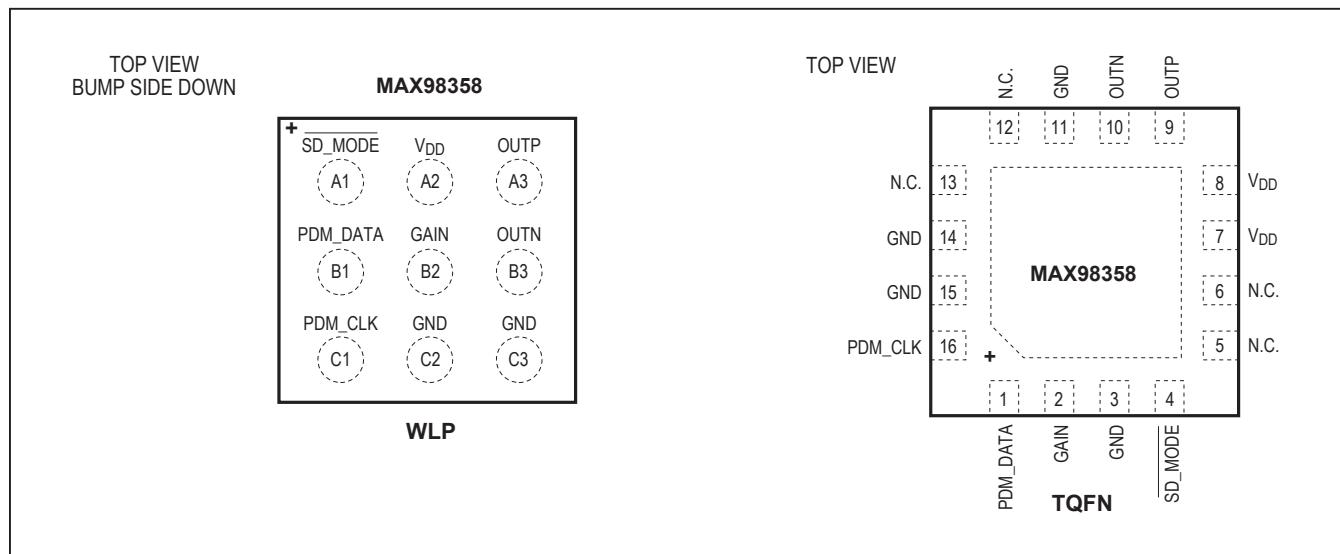

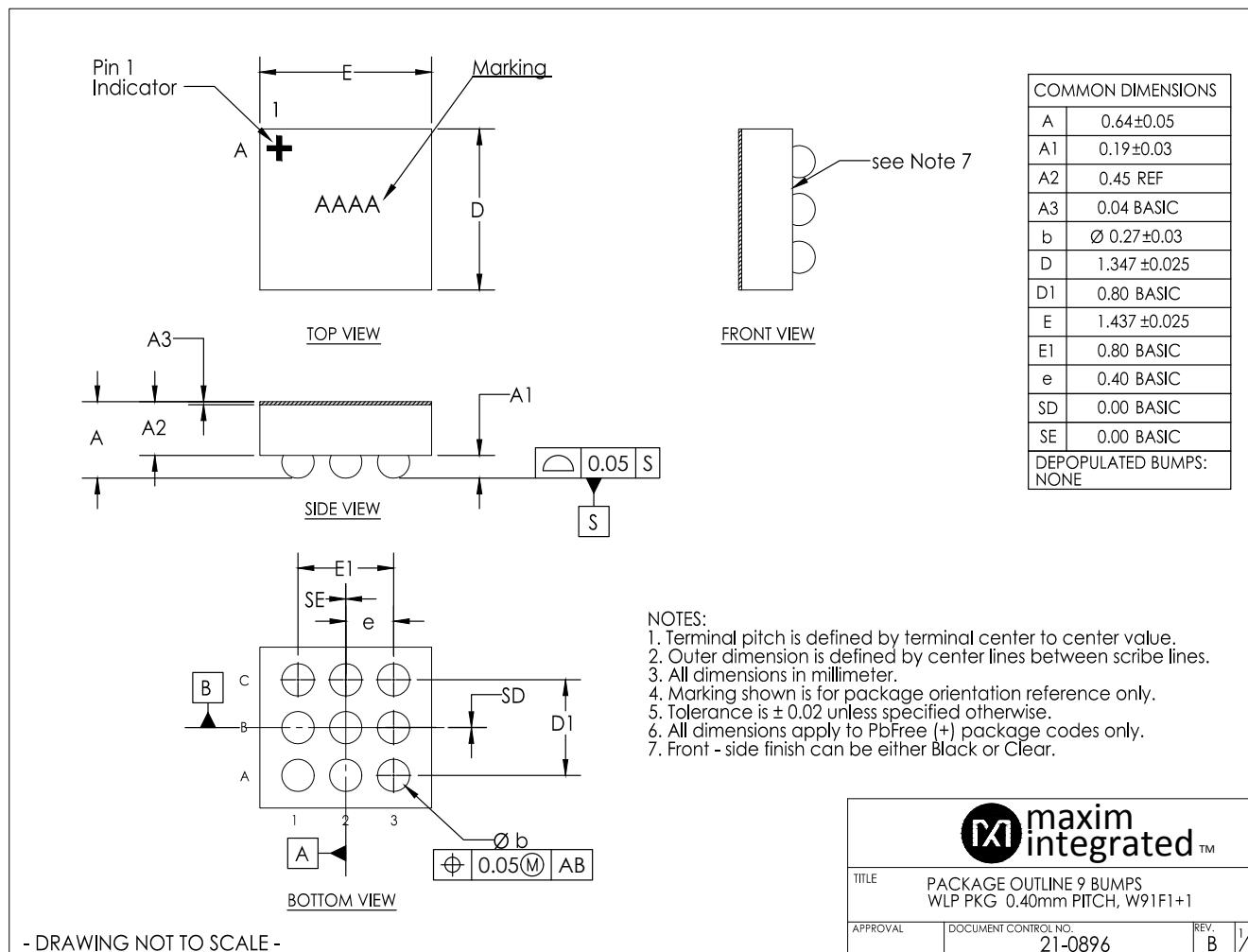

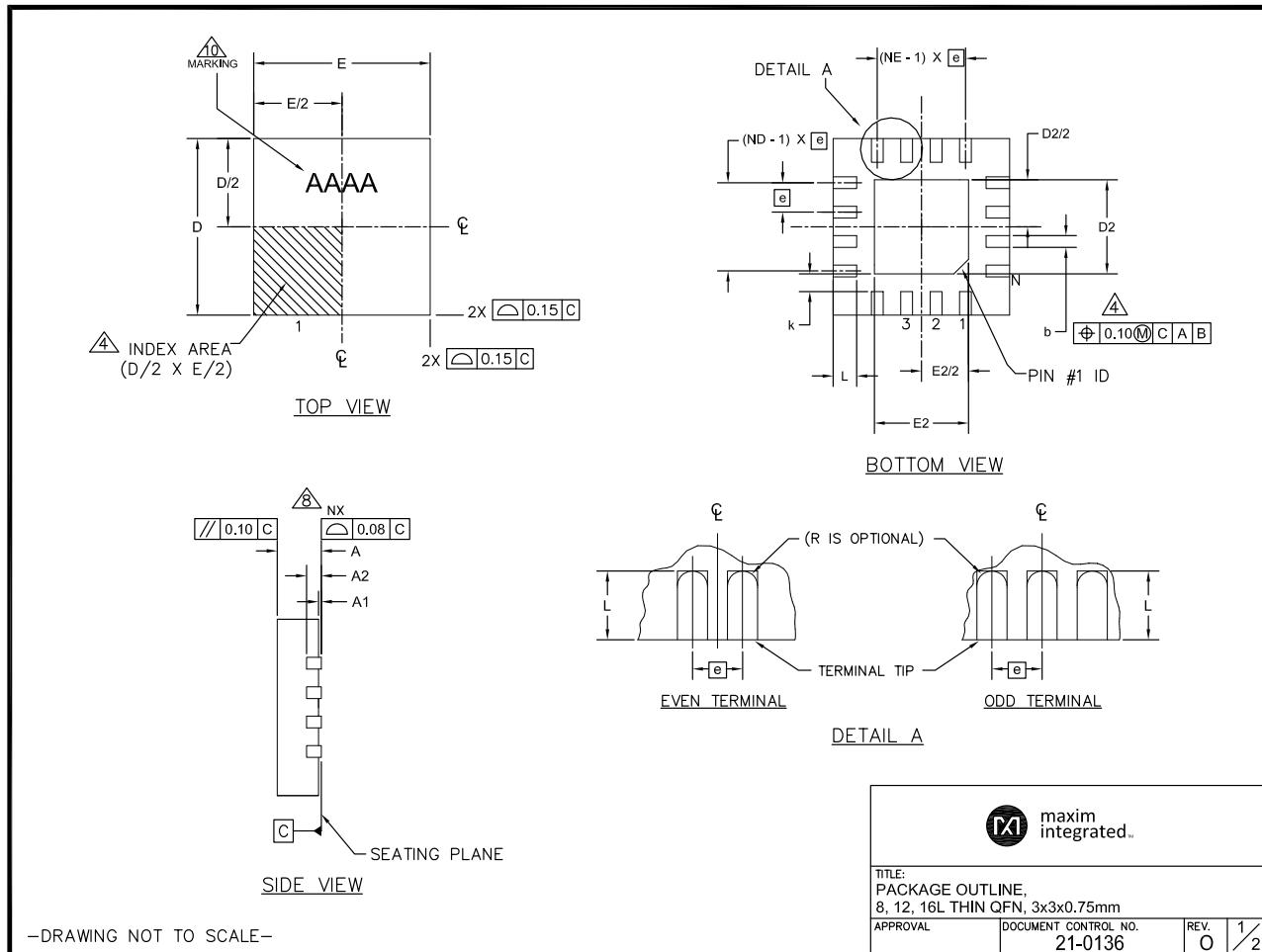

The IC is available in 9-pin WLP (1.345mm x 1.435mm x 0.64mm) and 16-pin TQFN (3mm x 3mm x 0.75mm) packages and is specified over the -40°C to +85°C temperature range.

### Applications

- Notebook and Netbook Computers

- Cellular Phones

- Tablets

- Portable Media Players

*Ordering Information and Functional Diagram appears at end of data sheet.*

### Features

- Single-Supply Operation (2.5V to 5.5V)

- 3.2W Output Power into 4Ω at 5V

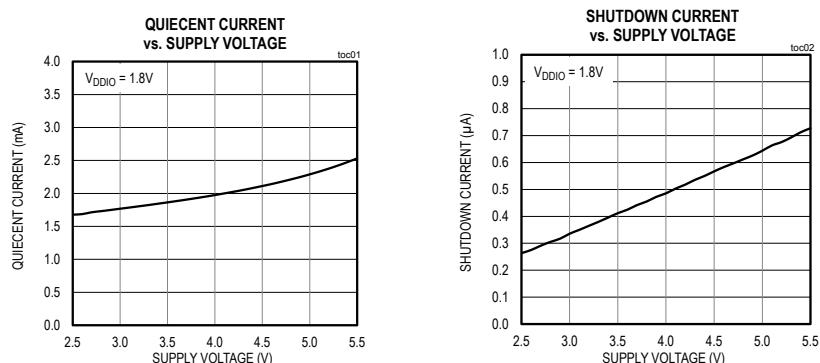

- 1.8mA Quiescent Current ( $V_{DD} = 3.7V$ )

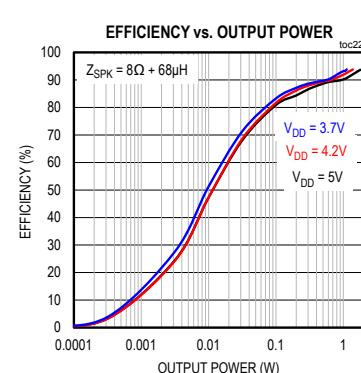

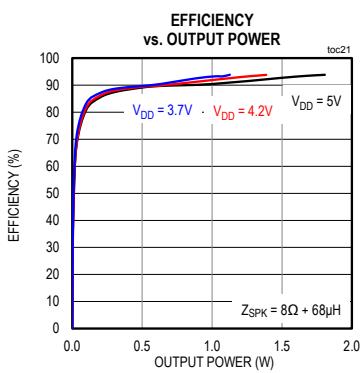

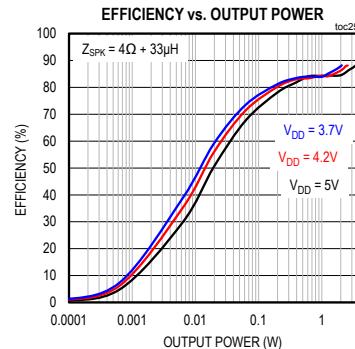

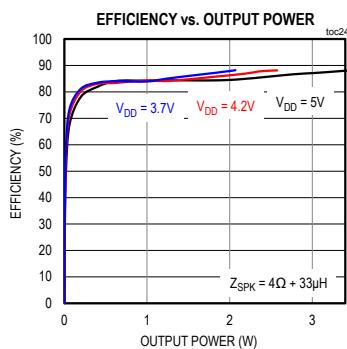

- 92% Efficiency ( $R_L = 8\Omega$ ,  $P_{OUT} = 1.5W$ )

- 29µVRMS Output Noise ( $A_V = 6dB$ )

- Low 0.015% THD+N at 1kHz

- Supported PDM\_CLK Rates of 1.84MHz–4.32MHz and 5.28MHz–8.64MHz

- Supports Left, Right, or Left/2 + Right/2 Outputs

- Sophisticated Edge Rate Control Enables Filterless Class D Outputs

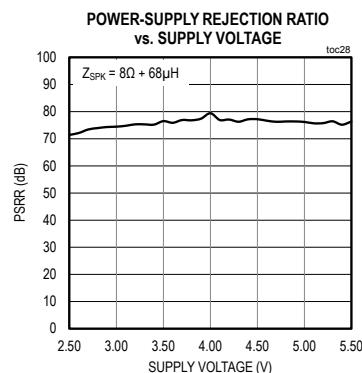

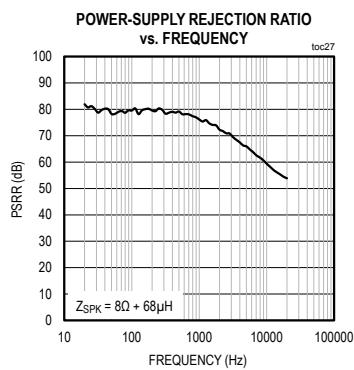

- 77dB PSRR at 217Hz

- Low RF Susceptibility Rejects TDMA Noise from GSM Radios

- Extensive Click-and-Pop Reduction Circuitry

- Robust Short-Circuit and Thermal Protection

- Available in Space-Saving Packages: 1.345mm x 1.435mm WLP (0.4mm Pitch) 3mm x 3mm TQFN

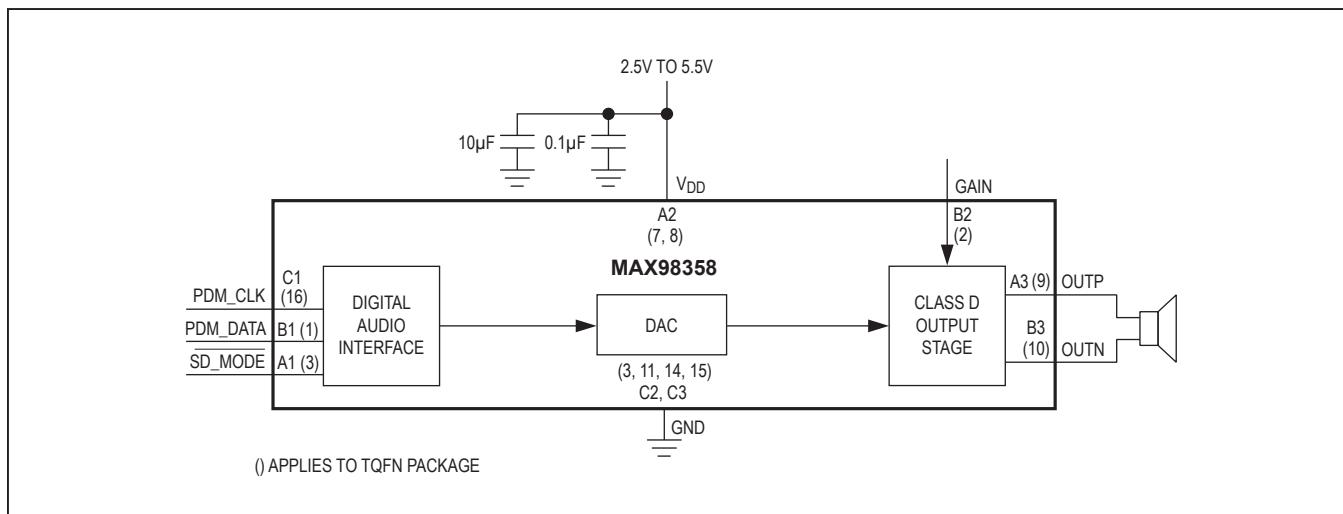

### Simplified Block Diagram

---

**TABLE OF CONTENTS**

---

|                                                 |    |

|-------------------------------------------------|----|

| General Description . . . . .                   | 1  |

| Applications . . . . .                          | 1  |

| Features . . . . .                              | 1  |

| Simplified Block Diagram . . . . .              | 1  |

| Absolute Maximum Ratings . . . . .              | 4  |

| Package Thermal Characteristics . . . . .       | 4  |

| Electrical Characteristics . . . . .            | 4  |

| Typical Operating Characteristics . . . . .     | 7  |

| General . . . . .                               | 7  |

| Speaker Amplifier . . . . .                     | 8  |

| Bump/Pin Configurations . . . . .               | 15 |

| Bump/Pin Description . . . . .                  | 15 |

| Detailed Description . . . . .                  | 16 |

| Digital Audio Interface . . . . .               | 16 |

| Supported PDM_CLK Rates . . . . .               | 16 |

| PDM_CLK Jitter Tolerance . . . . .              | 16 |

| PDM Timing Characteristics . . . . .            | 17 |

| Standby Mode . . . . .                          | 17 |

| SD_MODE Pin and Shutdown Operation . . . . .    | 17 |

| Class D Speaker Amplifier . . . . .             | 18 |

| Ultra-Low EMI Filterless Output Stage . . . . . | 18 |

| Speaker Current Limit . . . . .                 | 18 |

| Gain Selection . . . . .                        | 18 |

| Click-and-Pop Suppression . . . . .             | 18 |

| Filterless Class D Operation . . . . .          | 22 |

| Power-Supply Input . . . . .                    | 22 |

| Layout and Grounding . . . . .                  | 22 |

| WLP Applications Information . . . . .          | 22 |

| Functional Diagram . . . . .                    | 23 |

| Ordering Information . . . . .                  | 23 |

| Package Information . . . . .                   | 24 |

| Revision History . . . . .                      | 27 |

---

**LIST OF FIGURES**

---

|                                                                           |    |

|---------------------------------------------------------------------------|----|

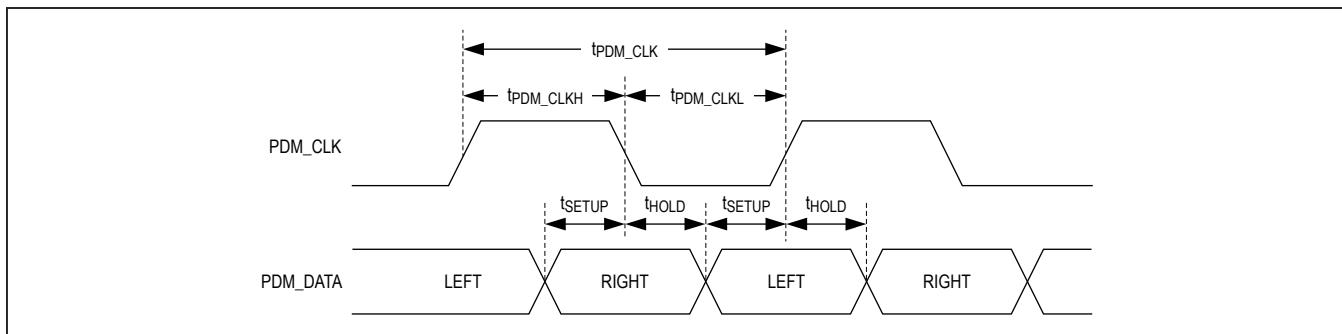

| Figure 1. PDM Audio Interface Timing Diagram .....                        | 7  |

| Figure 2. PDM Digital Audio Interface Timing .....                        | 17 |

| Figure 3. <u>SD_MODE</u> Resistor Connection Using Open-Drain Driver..... | 19 |

| Figure 4. <u>SD_MODE</u> Resistor Connection Using Push-Pull Driver ..... | 19 |

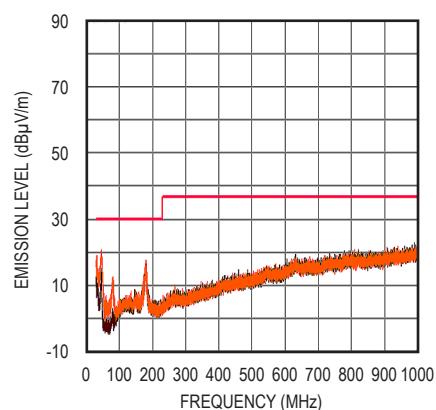

| Figure 5. EMI with 12in of Speaker Cable and No Output Filtering.....     | 19 |

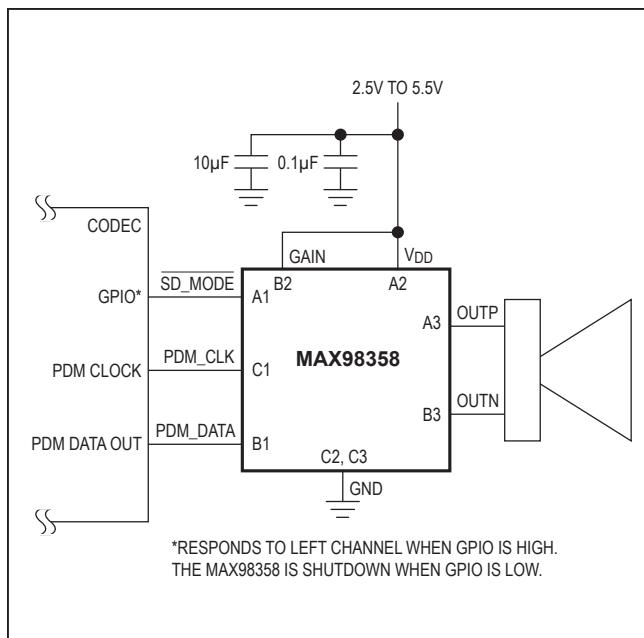

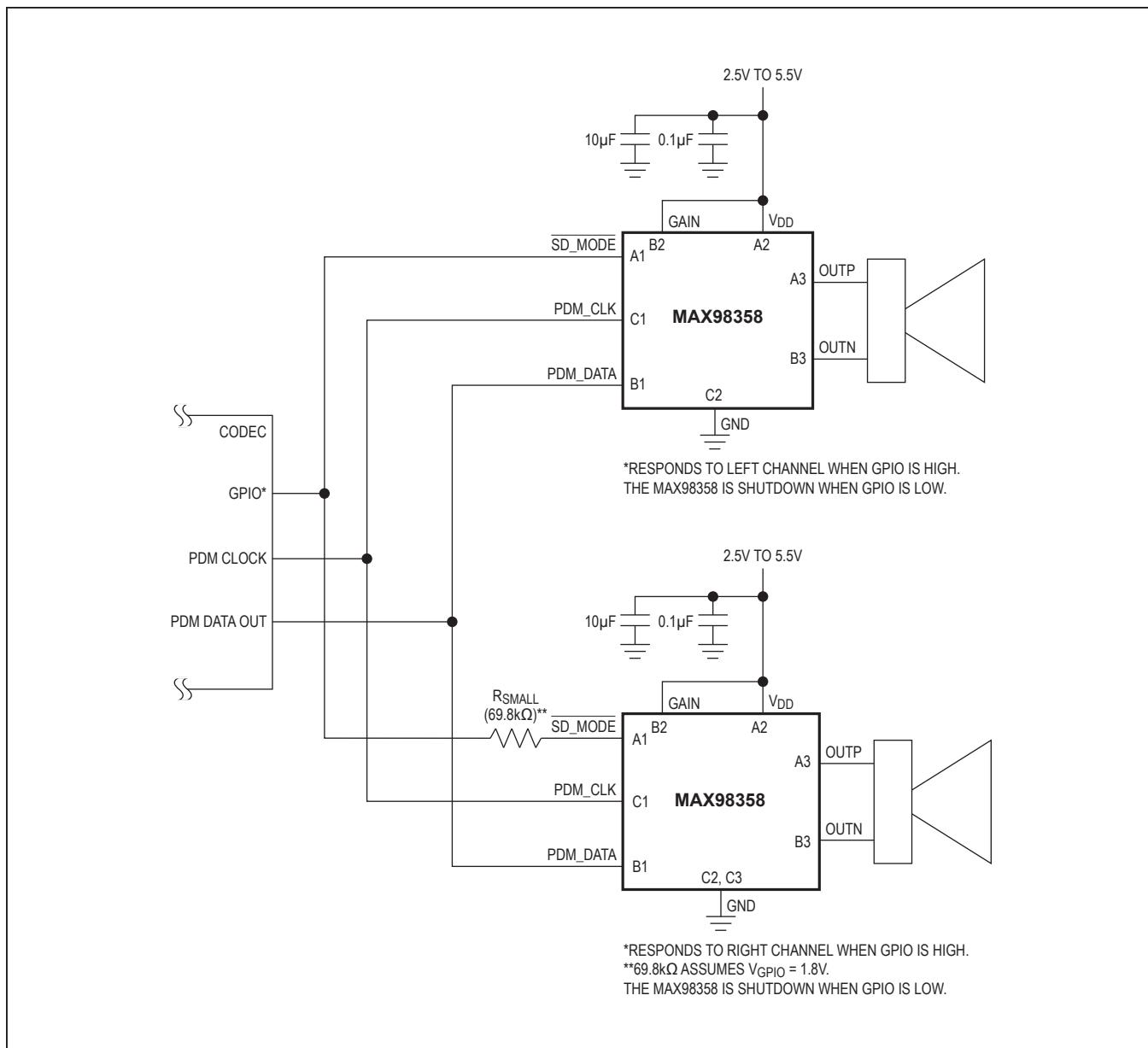

| Figure 6. Left-Channel Operation with 6dB Gain .....                      | 20 |

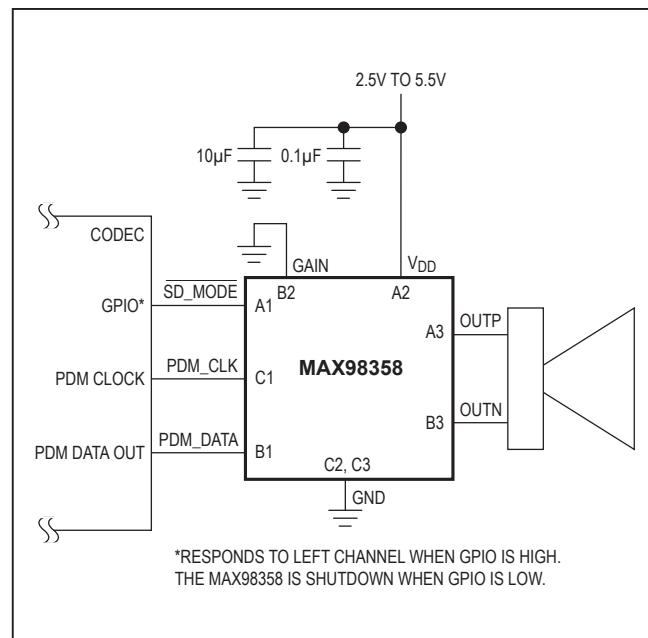

| Figure 8. Right-Channel Operation with 6dB Gain .....                     | 20 |

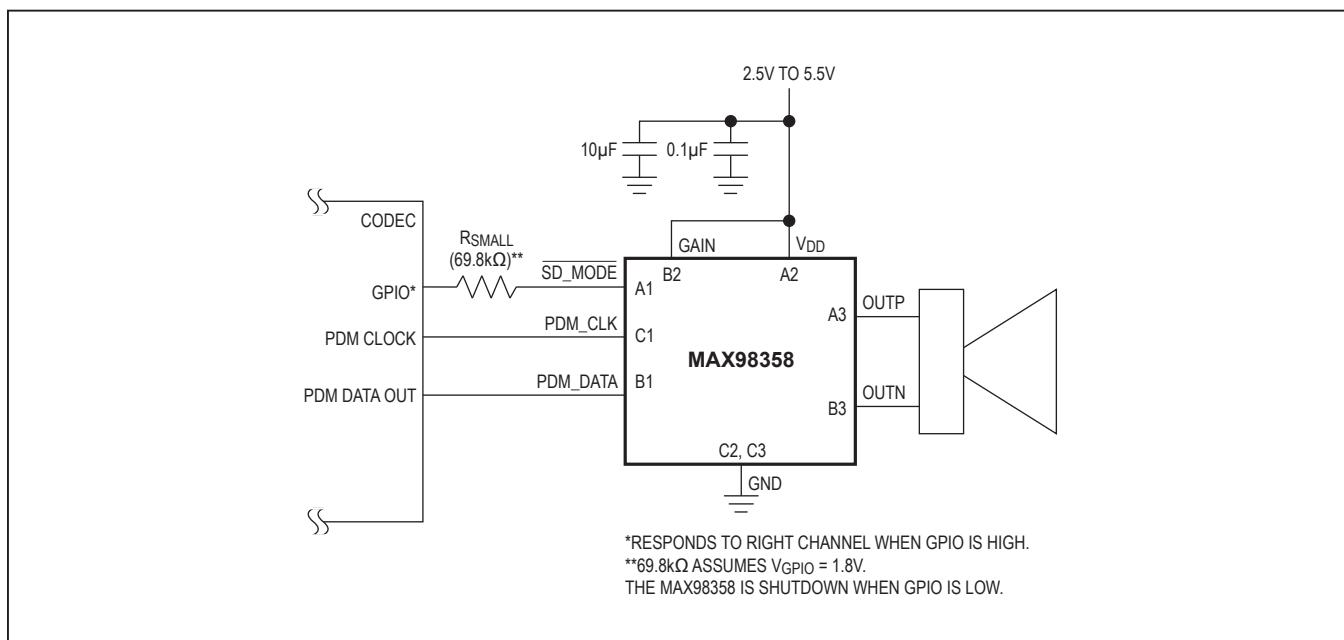

| Figure 7. Left-Channel Operation with 12dB Gain.....                      | 20 |

| Figure 9. Stereo Operation Using Two MAX98358s .....                      | 21 |

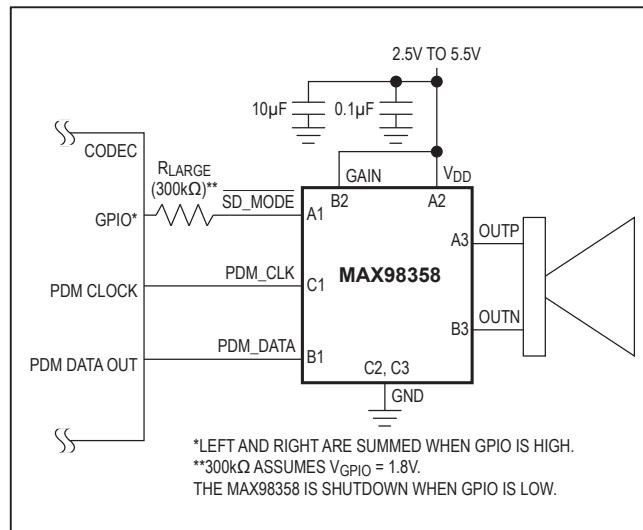

| Figure 10. Monomix (Left/2 + Right/2) PDM Operation with 6dB Gain.....    | 22 |

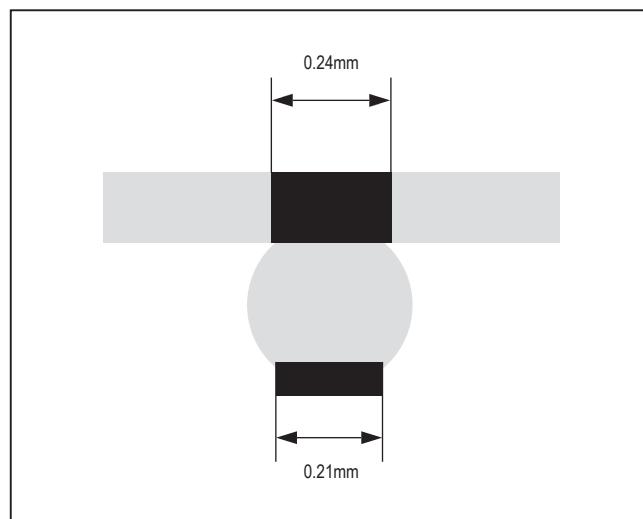

| Figure 11. MAX98358 WLP Ball Dimensions .....                             | 22 |

---

**LIST OF TABLES**

---

|                                                                 |    |

|-----------------------------------------------------------------|----|

| Table 1. PDM_CLK Channel Select.....                            | 16 |

| Table 2. PDM_CLK Rates .....                                    | 16 |

| Table 3. Calculated PDM_CLK Rates .....                         | 16 |

| Table 4. RMS Jitter Tolerance .....                             | 16 |

| Table 5. <u>SD_MODE</u> Control .....                           | 17 |

| Table 6. Examples of <u>SD_MODE</u> Pullup Resistor Values..... | 18 |

| Table 7. Gain Selection .....                                   | 18 |

## Absolute Maximum Ratings

$V_{DD}$ , PDM\_CLK and PDM\_DATA to GND ..... -0.3V to +6V

All Other Pins to GND ..... -0.3V to ( $V_{DD}$  + 0.3V)

Continuous Current In/Out of  $V_{DD}$ /GND/OUT\_ .....  $\pm 1.6A$

Continuous Input Current (all other pins) .....  $\pm 20mA$

Duration of OUT\_ Short Circuit to GND or  $V_{DD}$  ..... Continuous

Duration of OUTP Short to OUTN ..... Continuous

Continuous Power Dissipation ..... ( $T_A = +70^\circ C$ )

WLP (derate 13.7mW/ $^\circ C$  above  $+70^\circ C$ ) ..... 1096mW

TQFN (derate 20.8mW/ $^\circ C$  above  $+70^\circ C$ ) ..... 1666mW

Junction Temperature ..... +150 $^\circ C$

Operating Temperature Range ..... -40 $^\circ C$  to +85 $^\circ C$

Storage Temperature Range ..... -65 $^\circ C$  to +150 $^\circ C$

Soldering Temperature (reflow) ..... +230 $^\circ C$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Thermal Characteristics (Note 1)

WLP

- Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) ..... 73 $^\circ C/W$

- Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) ..... 50 $^\circ C/W$

TQFN

- Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) ..... 48 $^\circ C/W$

- Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) ..... 7 $^\circ C/W$

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

## Electrical Characteristics

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN =  $V_{DD}$  (+6dB), PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $Z_{SPK} = \infty$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                    | SYMBOL      | CONDITIONS                                                                     |                                           | MIN       | TYP       | MAX | UNITS   |

|------------------------------|-------------|--------------------------------------------------------------------------------|-------------------------------------------|-----------|-----------|-----|---------|

| Supply Voltage Range         | $V_{DD}$    | Guaranteed by PSSR test                                                        |                                           | 2.5       | 5.5       |     | V       |

| Undervoltage Lockout         | UVLO        |                                                                                |                                           | 1.4       | 1.8       | 2.3 | V       |

| Quiescent Current            | $I_{DD}$    | $T_A = +25^\circ C$                                                            |                                           | 2.2       | 2.7       |     | mA      |

|                              |             | $T_A = +25^\circ C$ , $V_{DD} = 3.7V$                                          |                                           | 1.8       | 2.2       |     |         |

| Shutdown Current             | $I_{SHDN}$  | $SD\_MODE = 0V$ , $T_A = +25^\circ C$                                          |                                           | 0.6       | 2         |     | $\mu A$ |

| Standby Current              | $I_{STNDY}$ | $SD\_MODE = 1.8V$ , no PDM_CLK, $T_A = +25^\circ C$                            |                                           | 340       | 400       |     | $\mu A$ |

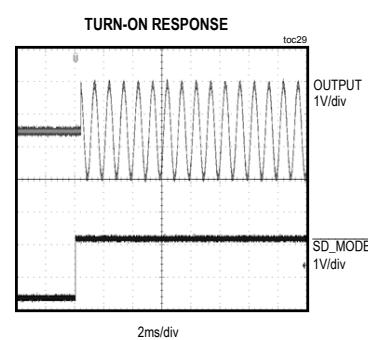

| Turn-On Time                 | $t_{ON}$    | Time from receipt of first clock cycle to full operation                       |                                           | 0.6       | 0.7       |     | ms      |

| Output Offset Voltage        | $V_{OS}$    | $T_A = +25^\circ C$ , gain = 15dB                                              |                                           | $\pm 0.3$ | $\pm 2.5$ |     | mV      |

| Click-and-Pop Level          | $K_{CP}$    | Peak voltage, $T_A = +25^\circ C$ , A-weighted, 32 samples per second (Note 3) | Into shutdown                             | -72       |           |     | dBV     |

|                              |             |                                                                                | Out of shutdown                           | -66       |           |     |         |

| Power-Supply Rejection Ratio | PSRR        | $V_{DD} = 2.5V$ to $5.5V$ , $T_A = +25^\circ C$                                |                                           | 60        | 75        |     | dB      |

|                              |             | $T_A = +25^\circ C$<br>(Notes 3, 4)                                            | $f = 217Hz$ , 200mV <sub>P-P</sub> ripple | 77        |           |     |         |

|                              |             |                                                                                | $f = 10kHz$ , 200mV <sub>P-P</sub> ripple | 60        |           |     |         |

## Electrical Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN =  $V_{DD}$  (+6dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $Z_{SPK} = \infty$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                                   | SYMBOL                | CONDITIONS                                                                                     | MIN                                              | TYP  | MAX  | UNITS             |

|---------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------|------|------|-------------------|

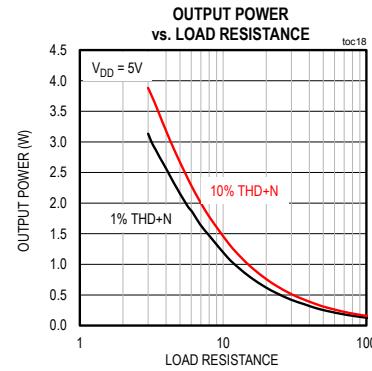

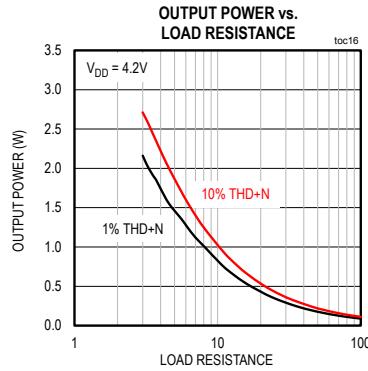

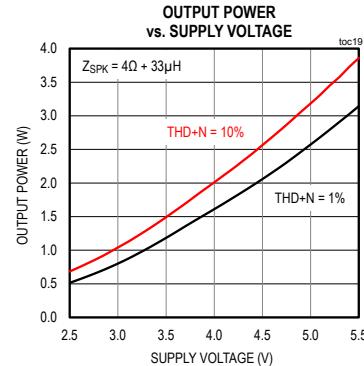

| Output Power (Note 3)                       | P <sub>OUT</sub>      | THD+N 10%                                                                                      | Z <sub>SPK</sub> = 4Ω + 33μH                     | 3.2  |      | W                 |

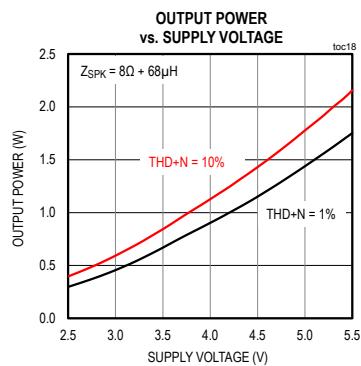

|                                             |                       |                                                                                                | Z <sub>SPK</sub> = 8Ω + 68μH                     | 1.8  |      |                   |

|                                             |                       |                                                                                                | Z <sub>SPK</sub> = 8Ω + 68μH,<br>$V_{DD} = 3.7V$ | 0.93 |      |                   |

|                                             |                       | THD+N = 1%                                                                                     | Z <sub>SPK</sub> = 4Ω + 33μH                     | 2.5  |      |                   |

|                                             |                       |                                                                                                | Z <sub>SPK</sub> = 8Ω + 68μH                     | 1.4  |      |                   |

|                                             |                       |                                                                                                | Z <sub>SPK</sub> = 8Ω + 68μH,<br>$V_{DD} = 3.7V$ | 0.77 |      |                   |

|                                             |                       |                                                                                                |                                                  |      |      |                   |

|                                             |                       |                                                                                                |                                                  |      |      |                   |

| Total Harmonic Distortion + Noise           | THD+N                 | f = 1kHz, P <sub>OUT</sub> = 1W, $T_A = +25^\circ C$ ,<br>$Z_{SPK} = 4\Omega + 33\mu H$ (WLP)  | 0.02                                             | 0.06 |      | %                 |

|                                             |                       | f = 1kHz, P <sub>OUT</sub> = 1W, $T_A = +25^\circ C$ ,<br>$Z_{SPK} = 4\Omega + 33\mu H$ (TQFN) | 0.02                                             |      |      |                   |

|                                             |                       | f = 1kHz, P <sub>OUT</sub> = 0.5W, $T_A = +25^\circ C$ ,<br>$Z_{SPK} = 8\Omega + 68\mu H$      | 0.013                                            |      |      |                   |

| Dynamic Range                               | DR                    | A-weighted, PDM_CLK = 6.144MHz,<br>$V_{RMS} = 2.54V$                                           | 99                                               |      |      | dB                |

| Output Noise                                | V <sub>N</sub>        | A-weighted (Note 4)                                                                            | 29                                               |      |      | μV <sub>RMS</sub> |

| Gain (Relative to a 2.1dBV Reference Level) | A <sub>V</sub>        | GAIN = GND through 100kΩ                                                                       | 14.4                                             | 15   | 15.6 | dB                |

|                                             |                       | GAIN = GND                                                                                     | 11.4                                             | 12   | 12.6 |                   |

|                                             |                       | GAIN = unconnected                                                                             | 8.4                                              | 9    | 9.6  |                   |

|                                             |                       | GAIN = $V_{DD}$                                                                                | 5.4                                              | 6    | 6.6  |                   |

|                                             |                       | GAIN = $V_{DD}$ through 100kΩ                                                                  | 2.4                                              | 3    | 3.6  |                   |

| Current Limit                               | I <sub>LIM</sub>      |                                                                                                | 2.8                                              |      |      | A                 |

| Efficiency                                  | h                     | Z <sub>SPK</sub> = 8Ω + 68μH, THD+N = 10%,<br>f = 1kHz, gain = 12dB                            | 92                                               |      |      | %                 |

| DAC Gain Error                              |                       |                                                                                                | 1                                                |      |      | %                 |

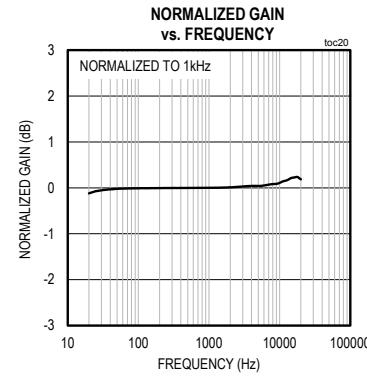

| Frequency Response                          |                       |                                                                                                | ±0.5                                             |      |      | dB                |

| Class D Oscillator Frequency                | f <sub>OOSC</sub>     |                                                                                                | 330                                              |      |      | kHz               |

| Spread-Spectrum Bandwidth                   |                       |                                                                                                | ±20                                              |      |      | kHz               |

| <b>DIGITAL AUDIO INTERFACE</b>              |                       |                                                                                                |                                                  |      |      |                   |

| PDM_CLK High Frequency Range                | f <sub>CLKH</sub>     |                                                                                                | 5.28                                             | 8.64 |      | MHz               |

| PDM_CLK Low Frequency Range                 | f <sub>CLKL</sub>     |                                                                                                | 1.84                                             | 4.32 |      | MHz               |

| PDM_CLK High Time                           | t <sub>PDM_CLKH</sub> |                                                                                                | 40                                               |      |      | ns                |

| PDM_CLK Low Time                            | t <sub>PDM_CLKL</sub> |                                                                                                | 40                                               |      |      | ns                |

| Maximum Low-Frequency PDM_CLK Jitter        |                       | RMS jitter below 40kHz                                                                         | 0.5                                              |      |      | ns                |

| Maximum Low-Frequency PDM_CLK Jitter        |                       | RMS jitter above 40kHz                                                                         | 12                                               |      |      | ns                |

## Electrical Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN =  $V_{DD}$  (+6dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $Z_{SPK} = \infty$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^\circ C$ .) (Note 2)

| PARAMETER                      | SYMBOL           | CONDITIONS                                      | MIN | TYP | MAX | UNITS   |

|--------------------------------|------------------|-------------------------------------------------|-----|-----|-----|---------|

| Input High Voltage             | $V_{IH}$         | Digital audio inputs                            | 1.3 |     |     | V       |

| Input Low Voltage              | $V_{IL}$         | Digital audio inputs                            |     |     | 0.6 | V       |

| Input Leakage Current          | $I_{IH}, I_{IL}$ | $V_{IN} = 0V, V_{DD} = 5.5V, T_A = +25^\circ C$ | -1  |     | +1  | $\mu A$ |

| Input Capacitance              | $C_{IN}$         |                                                 |     | 3   |     | pF      |

| PDM Ones Density               |                  | Maximum                                         |     | 75  |     | %       |

|                                |                  | Minimum                                         |     | 25  |     |         |

| PDM_DATA to PDM_CLK Setup Time | $t_{SETUP}$      |                                                 | 10  |     |     | ns      |

| PDM_DATA to PDM_CLK Hold Time  | $t_{HOLD}$       |                                                 | 10  |     |     |         |

### SD\_MODE COMPARATOR TRIP POINTS

|                           |          |                                                              |       |      |       |           |

|---------------------------|----------|--------------------------------------------------------------|-------|------|-------|-----------|

| B0                        |          | See $\overline{SD\_MODE}$ and shutdown operation for details | 0.08  | 0.16 | 0.355 | V         |

| B1                        |          |                                                              | 0.65  | 0.77 | 0.825 |           |

| B2                        |          |                                                              | 1.245 | 1.4  | 1.5   |           |

| SD_MODE Pulldown Resistor | $R_{PD}$ |                                                              | 92    | 100  | 108   | $k\Omega$ |

### GAIN COMPARATOR TRIP POINTS

|            |  |                   |                 |                 |   |

|------------|--|-------------------|-----------------|-----------------|---|

| $V_{GAIN}$ |  | $A_V = 3dB$ gain  | 0.65 x $V_{DD}$ | 0.85 x $V_{DD}$ | V |

|            |  | $A_V = 6dB$ gain  | 0.9 x $V_{DD}$  | $V_{DD}$        |   |

|            |  | $A_V = 9dB$ gain  | 0.4 x $V_{DD}$  | 0.6 x $V_{DD}$  |   |

|            |  | $A_V = 12dB$ gain | 0               | 0.1 x $V_{DD}$  |   |

|            |  | $A_V = 15dB$ gain | 0.15 x $V_{DD}$ | 0.35 x $V_{DD}$ |   |

**Note 2:** 100% production tested at  $T_A = +25^\circ C$ . Specifications over temperature limits are guaranteed by design.

**Note 3:** Class D amplifier testing performed with a resistive load in series with an inductor to simulate an actual speaker load. For  $R_L = 8\Omega$ ,  $L_L = 68\mu H$ . For  $R_L = 4\Omega$ ,  $L_L = 33\mu H$ .

**Note 4:** Digital silence used for input signal.

**Note 5:** Dynamic range is measured using the EIJA method. -60dbFS 1kHz output signal. A-weighted and normalized to 0dBFS.  $f = 20Hz$  to  $20kHz$ .

Figure 1. PDM Audio Interface Timing Diagram

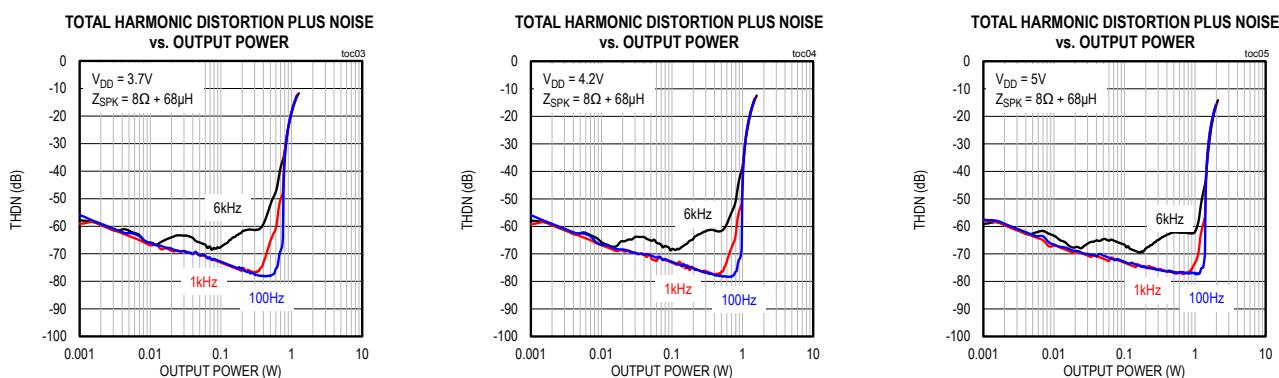

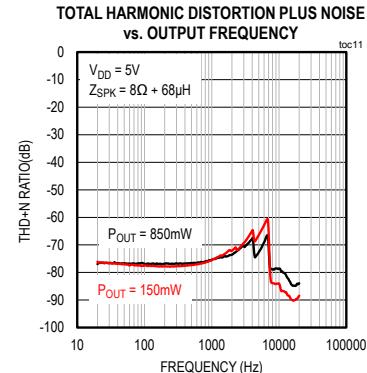

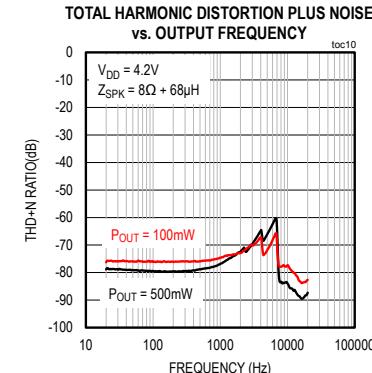

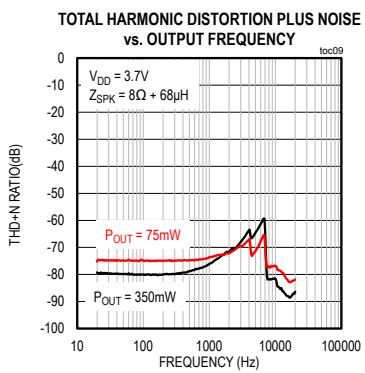

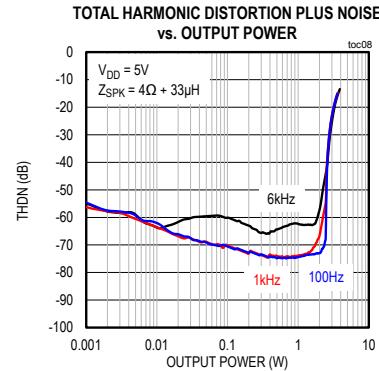

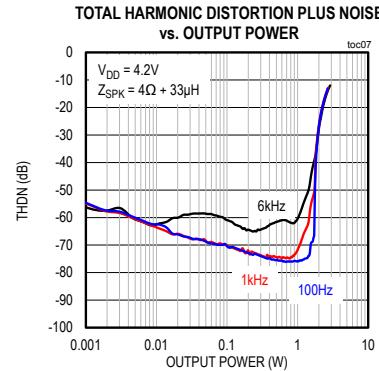

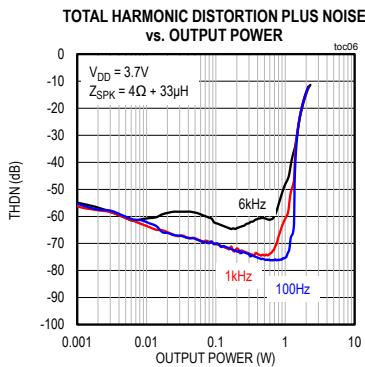

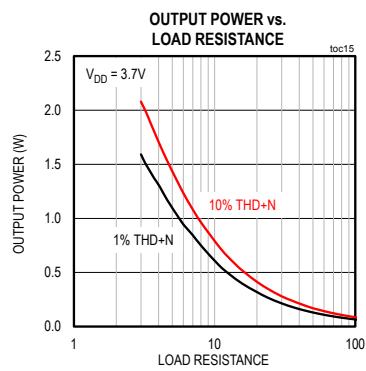

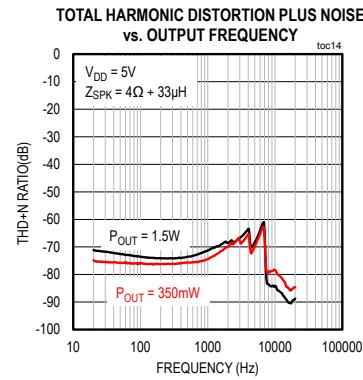

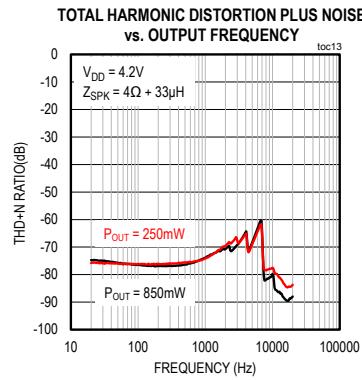

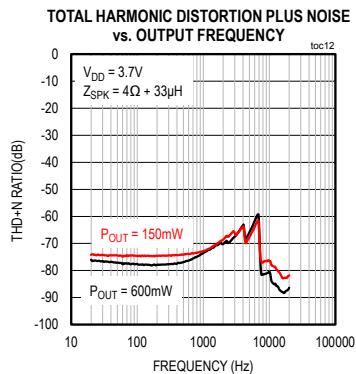

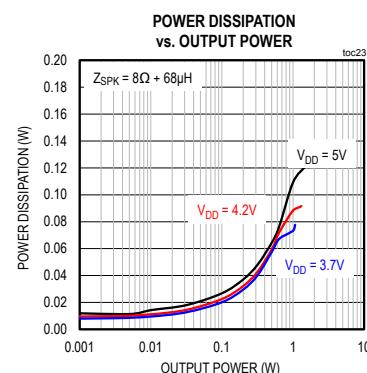

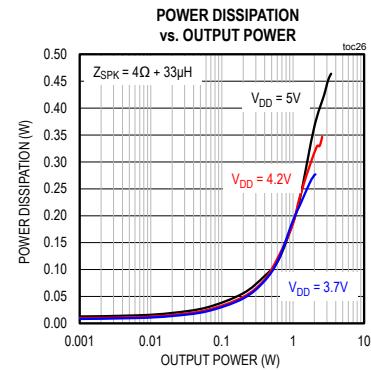

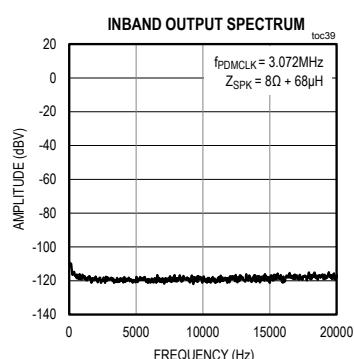

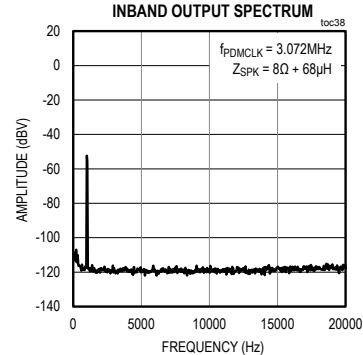

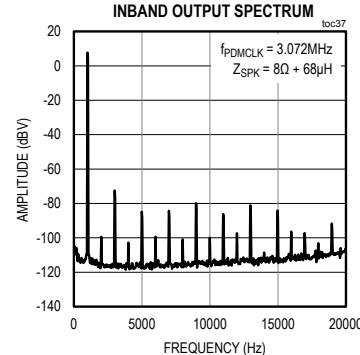

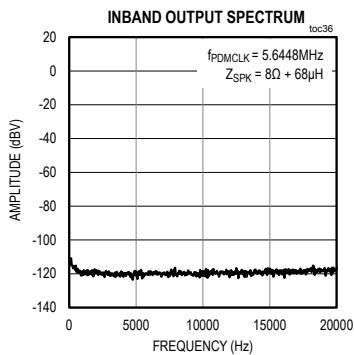

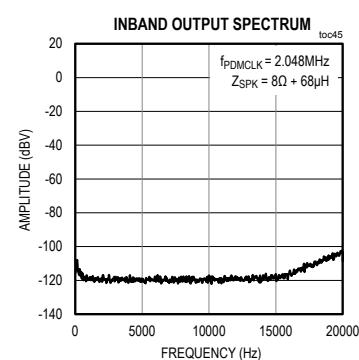

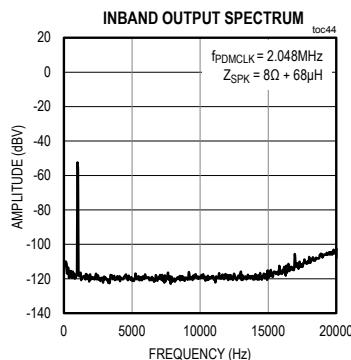

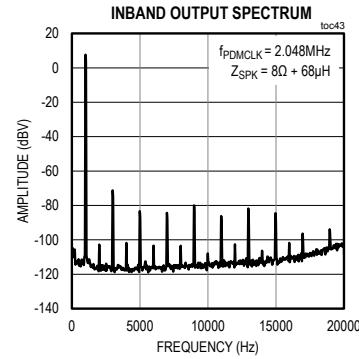

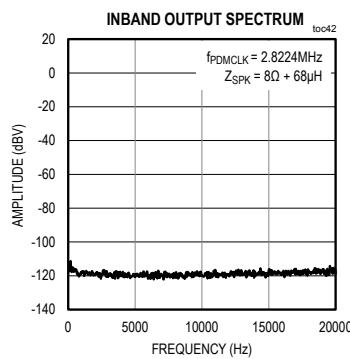

## Typical Operating Characteristics

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

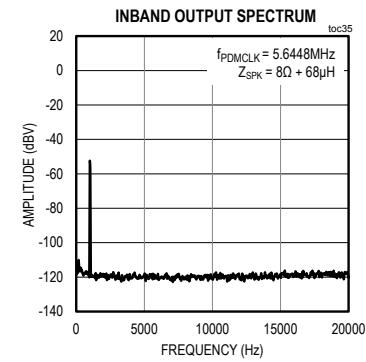

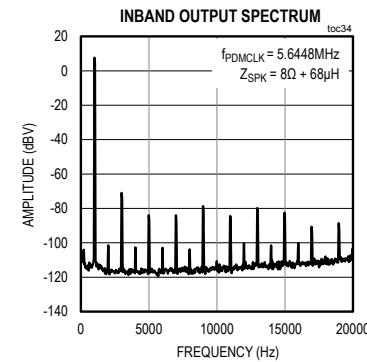

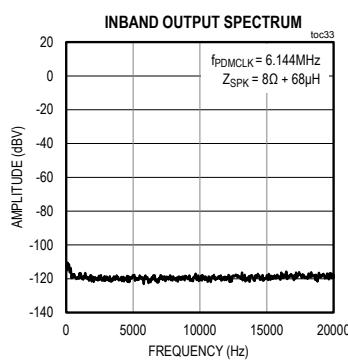

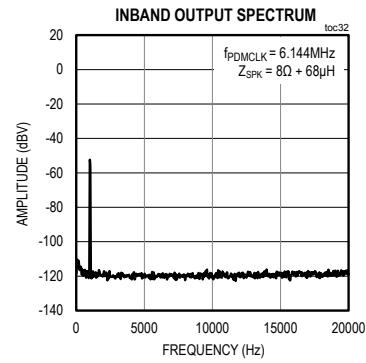

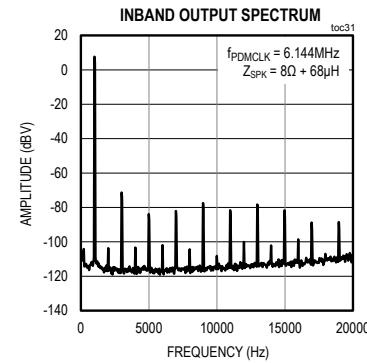

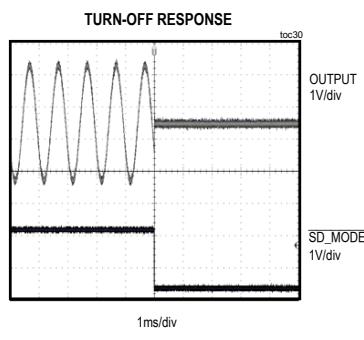

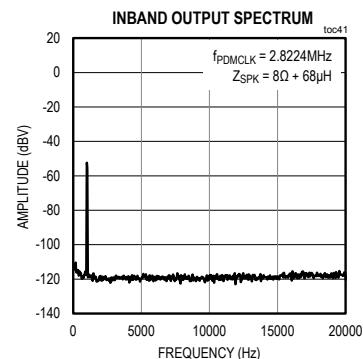

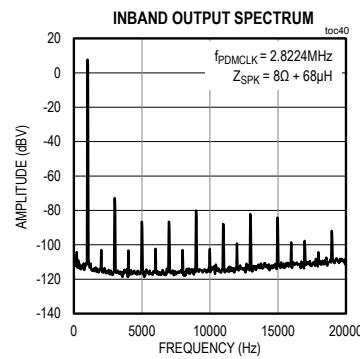

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

## Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ ,  $V_{GND} = 0V$ , GAIN = GND (12dB). PDM\_CLK = 3.072MHz, speaker loads ( $Z_{SPK}$ ) connected between OUTP and OUTN,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

## Bump/Pin Configurations

## Bump/Pin Description

| BUMP   | PIN           | NAME     | FUNCTION                                                                                                                           |    |

|--------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------|----|

| WLP    | TQFN          |          |                                                                                                                                    |    |

| A1     | 4             | SD_MODE  | Shutdown and Channel Select. Determines left, right, or (left/2 + right/2) mix and also used for shutdown. See Table 5.            |    |

| A2     | 7, 8          | VDD      | Power-Supply Input                                                                                                                 |    |

| A3     | 9             | OUTP     | Positive Speaker Amplifier Output                                                                                                  |    |

| B1     | 1             | PDM_DATA | Digital Input Signal                                                                                                               |    |

| B2     | 2             | GAIN     | Amplifier Gain                                                                                                                     |    |

|        |               |          | Gain Connections                                                                                                                   |    |

|        |               |          | GND through 100kΩ resistor                                                                                                         | 15 |

|        |               |          | GND                                                                                                                                | 12 |

|        |               |          | Unconnected                                                                                                                        | 9  |

|        |               |          | VDD                                                                                                                                | 6  |

|        |               |          | VDD through 100kΩ resistor                                                                                                         | 3  |

| B3     | 10            | OUTN     | Negative Speaker Amplifier Output                                                                                                  |    |

| C1     | 16            | PDM_CLK  | PDM Bit Clock Input Signal. Supports frequency ranges: 1.84MHz–4.32MHz and 5.28 MHz–8.64MHz.                                       |    |

| C2, C3 | 3, 11, 14, 15 | GND      | Ground                                                                                                                             |    |

| —      | 5, 6, 12, 13  | N.C.     | No Connection                                                                                                                      |    |

| —      | —             | EP       | Exposed Pad. The exposed pad is not internally connected. Connect the exposed pad to a solid ground plane for thermal dissipation. |    |

## Detailed Description

The MAX98358 is a digital PDM input Class D power amplifier. The PDM modulation scheme uses the relative density of digital pulses to represent the amplitude of an analog signal. The IC accepts stereo PDM data through PDM\_DATA and PDM\_CLK.

SD\_MODE selects which audio channel is output by the amplifier and is used to put the IC into shutdown. The GAIN pin offers five gain settings and allows the output of the amplifier to be tuned to the appropriate level.

**Table 1. PDM\_CLK Channel Select**

| PDM_CLK EDGE DIRECTION | CHANNEL |

|------------------------|---------|

| Rising edge            | Left    |

| Falling edge           | Right   |

**Table 2. PDM\_CLK Rates**

| SUPPORTED CLOCK RATES (MHz) |

|-----------------------------|

| 1.84–4.32                   |

| 5.28–8.64                   |

**Table 3. Calculated PDM\_CLK Rates**

| BASEBAND SAMPLE RATE (kHz) | INPUT CLOCK RATES (MHz) |                     |                      |                      |

|----------------------------|-------------------------|---------------------|----------------------|----------------------|

|                            | 32x OVERSAMPLED PDM     | 64x OVERSAMPLED PDM | 128x OVERSAMPLED PDM | 256x OVERSAMPLED PDM |

| 8                          | —                       | —                   | —                    | 2.048                |

| 16                         | —                       | —                   | 2.048                | 4.096                |

| 32                         | —                       | 2.048               | 4.096                | —                    |

| 44.1                       | —                       | 2.8224              | 5.6448*              | —                    |

| 48                         | —                       | 3.072               | 6.144*               | —                    |

| 88.2                       | 2.8224                  | 5.6448*             | —                    | —                    |

| 96                         | 3.072                   | 6.144*              | —                    | —                    |

\*The mono left/2 + right/2 feature is not supported at PDM\_CLK rates of 5.28MHz and above.

**Table 4. RMS Jitter Tolerance**

| FREQUENCY     | RMS JITTER TOLERANCE (ns) |

|---------------|---------------------------|

| < 40kHz       | 0.5                       |

| 40kHz–PDM_CLK | 12                        |

The output stage features low-quiescent current, comprehensive click-and-pop suppression, and excellent RF immunity. The IC offers Class AB audio performance with Class D efficiency in a minimal board-space solution. The Class D amplifier features spread-spectrum modulation with edge-rate and overshoot control circuitry that offers significant improvements in switch-mode amplifier radiated emissions. The amplifier features click-and-pop suppression that reduces audible transients on startup and shutdown. The amplifier includes thermal-overload and short-circuit protection.

## Digital Audio Interface

The IC takes a stereo PDM input signal directly into the DAC. Data read on the rising edge of PDM\_CLK is left-channel data while data read on the falling PDM\_CLK edge is right channel (Table 1).

## Supported PDM\_CLK Rates

Table 2 indicates the range of PDM\_CLK rates that are supported by the IC. Table 3 indicates the specific clock rates to use based on the baseband rate and the oversample rate of the incoming PDM signal.

## PDM\_CLK Jitter Tolerance

The IC features a very high PDM\_CLK jitter tolerance of 0.5ns for RMS jitter below 40kHz and 12ns for wideband RMS jitter while maintaining a dynamic range greater than 98dB (Table 4).

### PDM Timing Characteristics

Figure 2 shows the PDM operation of the IC. The bit-depth is one bit and each bit alternates between left-channel and right-channel data.

If the PDM generator produces data that is stuck at logic-high or logic-low, then the output of the IC is railed, forcing DC at the load. Therefore, it is recommended that the PDM generator includes protection to detect this invalid condition. If such a condition is detected, then the IC should either be put into shutdown or PDM\_CLK should be stopped.

### Standby Mode

The MAX98358 automatically enters standby mode when PDM\_CLK is removed. In standby mode, the Class D speaker amplifier is turned off and the outputs go into a high-impedance state, ensuring that the unwanted current is not transferred to the load during this condition. Standby mode should not be used in place of the shutdown mode because the shutdown mode provides the lowest power consumption and the best power-on/off click-and-pop performance.

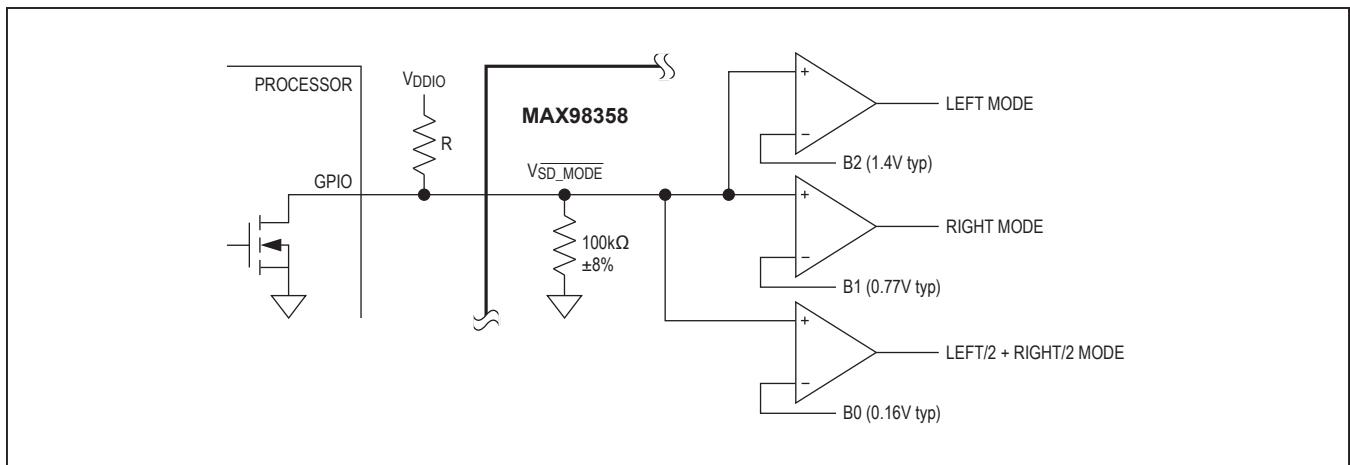

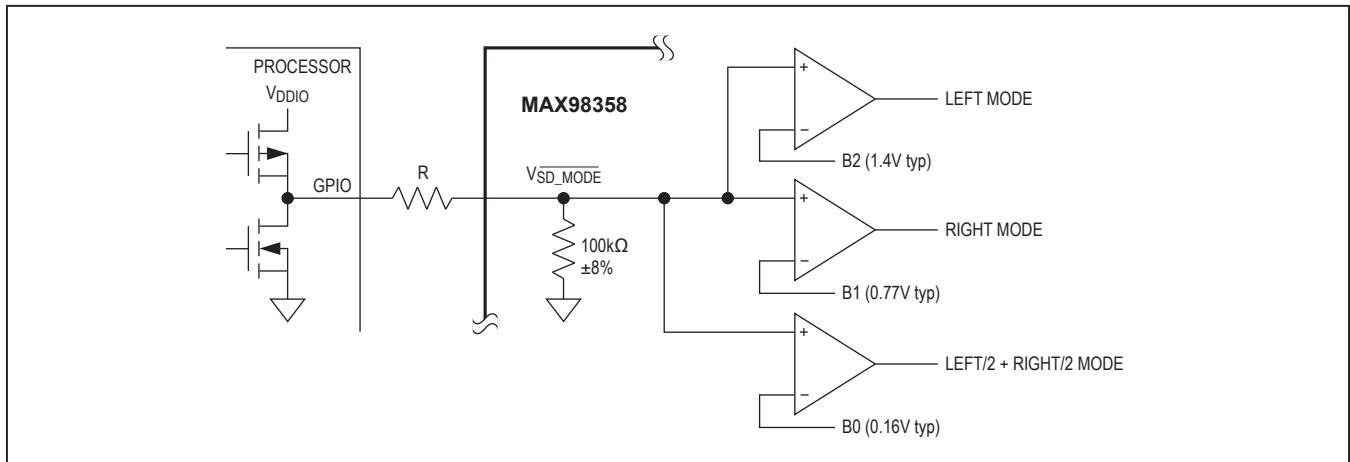

### SD\_MODE Pin and Shutdown Operation

The IC features a low-power shutdown mode, drawing less than  $0.6\mu\text{A}$  (typ) of supply current. During shutdown, all internal blocks are turned off, including setting the output stage to a high-impedance state. Drive SD\_MODE low to put the IC into shutdown.

The state of SD\_MODE determines the audio channel that is sent to the amplifier output (Table 5).

Drive SD\_MODE high to select the left channel of the stereo input data. Drive SD\_MODE high through a sufficiently small resistor to select the right channel of the stereo input data. Drive SD\_MODE high through a sufficiently large resistor to select monomix mode where both the left and right words of the stereo input data are summed (left/2 + right/2). The monomix (left/2 + right/2) mode is not supported for PDM\_CLK rates 5.28MHz. and above. RLARGE and RSMALL are determined by the VDDIO voltage (logic voltage from control interface) that is driving SD\_MODE according to the following two equations:

$$R_{\text{SMALL}} (\text{k}\Omega) = 94.0 \times V_{\text{DDIO}} - 100$$

$$R_{\text{LARGE}} (\text{k}\Omega) = 222.2 \times V_{\text{DDIO}} - 100$$

Figure 2. PDM Digital Audio Interface Timing

Table 5. SD\_MODE Control

| SD_MODE STATUS                      |                                                                       | SELECTED CHANNEL   |

|-------------------------------------|-----------------------------------------------------------------------|--------------------|

| High                                | $V_{\text{SD\_MODE}} > B_2$ trip point                                | Left               |

| Pullup through $R_{\text{SMALL}}$   | $B_2$ trip point (1.4V typ) $> V_{\text{SD\_MODE}} > B_1$ trip point  | Right              |

| Pullup through $R_{\text{LARGE}}^*$ | $B_1$ trip point (0.77V typ) $> V_{\text{SD\_MODE}} > B_0$ trip point | (Left/2 + right/2) |

| Low                                 | $B_0$ trip point (0.16V typ) $> V_{\text{SD\_MODE}}$                  | Shutdown           |

[Figure 3](#) and [Figure 4](#) show how to connect an external resistor to SD\_MODE when using an open-drain driver or a pullup/down driver.

When the device is configured in left channel mode (SD\_MODE is directly driven to logic-high by the control interface) care must be taken to avoid violating the Absolute Maximum Ratings limits for SD\_MODE. Ensuring that  $V_{DD}$  is always greater than  $V_{DDIO}$  is one way to prevent SD\_MODE from violating the Absolute Maximum Ratings limits. If this is not possible in the application (e.g., if  $V_{DD} < 3.0V$  and  $V_{DDIO} = 3.3V$ ), then it is necessary to add a small resistance ( $\sim 2k\Omega$ ) in series with SD\_MODE to limit the current into the SD\_MODE pin. This is not a concern when using the right channel or monomix modes.

### Class D Speaker Amplifier

The filterless Class D amplifier offers much higher efficiency than Class AB amplifiers. The high efficiency of a Class D amplifier is due to the switching operation of the output stage transistors. Any power loss associated with the Class D output stage is mostly due to the I<sub>2</sub>R loss of the MOSFET on-resistance and quiescent current overhead.

### Ultra-Low EMI Filterless Output Stage

Traditional Class D amplifiers require the use of external LC filters, or shielding, to meet EN55022B electromagnetic-interference (EMI) regulation standards. Maxim's active emissions-limiting edge-rate control circuitry and spread-spectrum modulation reduces EMI emissions while maintaining up to 92% efficiency.

Maxim's spread-spectrum modulation mode flattens wideband spectral components while proprietary techniques ensure that the cycle-to-cycle variation of the switching period does not degrade audio reproduction or efficiency. The ICs' spread-spectrum modulator randomly varies the switching frequency by  $\pm 20\text{kHz}$  around the center frequency (330kHz). Above 10MHz, the wideband spectrum looks like noise for EMI purposes ([Figure 5](#)).

### Speaker Current Limit

If the output current of the speaker amplifier exceeds the current limit (2.8A typ), the IC disables the outputs for approximately 100 $\mu\text{s}$ . At the end of the 100 $\mu\text{s}$ , the outputs are re-enabled. If the fault condition still exists, the IC continues to disable and re-enable the outputs until the fault condition is removed.

### Gain Selection

The IC offers five programmable gain selections through a singel gain input (GAIN). Gain is referenced to the full-scale output of the DAC, which is 2.1dBV ([Table 7](#)). Assuming that the desired output swing is not limited by the supply voltage rail, the IC's output level can be calculated based on the PDM input one's density and selected amplifier gain according to the following equation:

$$\text{Output signal level (dBV)} = 20 \times \log[\text{abs}(\text{PDM one's density}(\%)) - 50] / 25] \text{ (dBFS)} + 2.1\text{dB} + \text{selected speaker amplifier gain (dB)}$$

where the one's density of the PDM input ranges from 75% (maximum positive magnitude) to 25% (maximum negative magnitude). 0dBFS is referenced to 0dBV.

### Click-and-Pop Suppression

The IC speaker amplifier features Maxim's comprehensive click-and-pop suppression. During startup, the click-and-pop suppression circuitry reduces audible transient sources internal to the device. To achieve optimal click-and-pop reduction at startup, it is recommended that idle data be sent to the digital audio interface for the first 0.5ms of turn-on time. When entering shutdown, the differential speaker outputs simultaneously drop to GND.

**Table 6. Examples of SD\_MODE Pullup Resistor Values**

| LOGIC VOLTAGE LEVEL ( $V_{DDIO}$ ) (V) | $R_{SMALL}$ ( $k\Omega$ ) | $R_{LARGE}$ ( $k\Omega$ ) |

|----------------------------------------|---------------------------|---------------------------|

| 1.8                                    | 69.8                      | 300                       |

| 3.3                                    | 210                       | 634                       |

**Table 7. Gain Selection**

| GAIN                                                      | GAIN (dB) |

|-----------------------------------------------------------|-----------|

| Connect to GND through $100k\Omega \pm 5\%$ resistor      | 15        |

| Connect to GND                                            | 12        |

| Unconnected                                               | 9         |

| Connect to $V_{DD}$                                       | 6         |

| Connect to $V_{DD}$ through $100k\Omega \pm 5\%$ resistor | 3         |

Figure 3. SD\_MODE Resistor Connection Using Open-Drain DriverFigure 4. SD\_MODE Resistor Connection Using Push-Pull Driver

Figure 5. EMI with 12in of Speaker Cable and No Output Filtering

Figure 6. Left-Channel Operation with 6dB Gain

Figure 7. Left-Channel Operation with 12dB Gain

Figure 8. Right-Channel Operation with 6dB Gain

Figure 9. Stereo Operation Using Two MAX98358s

## Filterless Class D Operation

Traditional Class D amplifiers require an output filter to recover the audio signal from the amplifier's output. The filter adds cost, size, and decreases efficiency and THD+N performance. The MAX98358's filterless modulation scheme does not require an output filter. The device relies on the inherent inductance of the speaker coil and the natural filtering of both the speaker and the human ear to recover the audio component of the square-wave output.

Because the switching frequency of the IC is well beyond the bandwidth of most speakers, voice coil movement due to the switching frequency is very small. Use a speaker with a series inductance  $> 10\mu\text{H}$ . Typical  $8\Omega$  speakers exhibit series inductances in the  $20\mu\text{H}$  to  $100\mu\text{H}$  range.

## Power-Supply Input

$V_{DD}$ , which ranges from 2.5V to 5.5V, powers the IC, including the speaker amplifier. Bypass  $V_{DD}$  with a  $0.1\mu\text{F}$  and  $10\mu\text{F}$  capacitor to GND. Some applications might require only the  $10\mu\text{F}$  bypass capacitor, making it possible to operate with a single external component. Apply additional bulk capacitance at the IC if long input traces between  $V_{DD}$  and the power source are used.

## Layout and Grounding

Proper layout and grounding are essential for optimum performance. Good grounding improves audio performance and prevents switching noise from coupling into the audio signal.

Use wide, low-resistance output traces. As load impedance decreases, the current drawn from the device outputs increases. At higher current, the resistance of the output traces decreases the power delivered to the load. For example, if 2W is delivered from the speaker output to a  $4\Omega$  load through  $100\text{m}\Omega$  of total speaker trace, 1.904W is being delivered to the speaker. If power is delivered through  $10\text{m}\Omega$  of total speaker trace, 1.951W is being delivered to the speaker. Wide output, supply, and ground traces also improve the power dissipation of the IC. Parasitic capacitance on the output causes higher quiescent current by  $V_{DD} \times 330\text{kHz} \times C_{PARASITIC}$ .

For example, at  $V_{DD}$  and a total parasitic capacitance of  $100\text{pF}$  ( $50\text{pF}$  on each output trace), the increase in quiescent current is:  $5 \times 330\text{kHz} \times 100\text{pF} = 165\mu\text{A}$ .

The IC is inherently designed for excellent RF immunity. For best performance, add ground fills around all signal traces on top or bottom PCB planes.

## WLP Applications Information

For the latest application details on WLP construction, dimensions, tape carrier information, PCB techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to the Application Note 1891: *Wafer-Level Packaging (WLP) and Its Applications*. [Figure 11](#) shows the dimensions of the WLP balls used on the IC.

Figure 10. Monomix (Left/2 + Right/2) PDM Operation with 6dB Gain

Figure 11. MAX98358 WLP Ball Dimensions

## Functional Diagram

## Ordering Information

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX98358EWL+T | -40°C to +85°C | 9 WLP       |

| MAX98358ETE+  | -40°C to +85°C | 16 TQFN     |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

## Package Information

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.             | LAND PATTERN NO.                               |

|--------------|--------------|-------------------------|------------------------------------------------|

| 9 WLP        | W91F1+1      | <a href="#">21-0896</a> | Refer to <a href="#">Application Note 1891</a> |

| 16 TQFN      | T1633+4      | <a href="#">21-0136</a> | <a href="#">90-0031</a>                        |

## Package Information (continued)

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

## Package Information (continued)

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PKG  | 8L 3x3    |      |      | 12L 3x3   |      |      | 16L 3x3   |      |      |

|------|-----------|------|------|-----------|------|------|-----------|------|------|

| REF. | MIN.      | NOM. | MAX. | MIN.      | NOM. | MAX. | MIN.      | NOM. | MAX. |

| A    | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 |

| b    | 0.25      | 0.30 | 0.35 | 0.20      | 0.25 | 0.30 | 0.20      | 0.25 | 0.30 |

| D    | 2.90      | 3.00 | 3.10 | 2.90      | 3.00 | 3.10 | 2.90      | 3.00 | 3.10 |

| E    | 2.90      | 3.00 | 3.10 | 2.90      | 3.00 | 3.10 | 2.90      | 3.00 | 3.10 |

| e    | 0.65 BSC. |      |      | 0.50 BSC. |      |      | 0.50 BSC. |      |      |

| L    | 0.35      | 0.55 | 0.75 | 0.45      | 0.55 | 0.65 | 0.30      | 0.40 | 0.50 |

| N    | 8         |      |      | 12        |      |      | 16        |      |      |

| ND   | 2         |      |      | 3         |      |      | 4         |      |      |

| NE   | 2         |      |      | 3         |      |      | 4         |      |      |

| A1   | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 |

| A2   | 0.20 REF  |      |      | 0.20 REF  |      |      | 0.20 REF  |      |      |

| k    | 0.25      | -    | -    | 0.25      | -    | -    | 0.25      | -    | -    |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |             |        |  |

|------------------------|------|------|------|------|------|------|-------------|--------|--|

| PKG,<br>CODES          | D2   |      |      | E2   |      |      | PIN ID      | JEDEC  |  |

|                        | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |             |        |  |

| TQ833-1                | 0.25 | 0.70 | 1.25 | 0.25 | 0.70 | 1.25 | 0.35 x 45°  | WEEC   |  |

| T1233-1                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1233-3                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |

| T1633-2                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633-2C               | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633F-3               | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |

| T1633FH-3              | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |

| T1633-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633-4C               | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| T1633MK-5              | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |      |        |      |

|------------------------|------|------|------|------|------|------|------|--------|------|

| PKG<br>CODES           | D2   |      |      | E2   |      |      | L    | PIN ID |      |

|                        | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |      |        |      |

| T1233-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 | 0.45   | 0.55 |

| T1633-5                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.25 | 0.35   | 0.45 |

| T1633-5C               | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.25 | 0.35   | 0.45 |

NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

5. DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220 REVISION C. T1233-4, T1633-5 AND T1633-5C WITH CUSTOM LEAD DIMENSION.

10. MARKING SHOWN IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

11. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

12. WARPAGE NOT TO EXCEED 0.10mm.

13. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND Pb FREE (+) PARTS.

-DRAWING NOT TO SCALE-

|                                                                                                         |                                 |

|---------------------------------------------------------------------------------------------------------|---------------------------------|

|  maxim integrated™ |                                 |

| TITLE:<br>PACKAGE OUTLINE,<br>8, 12, 16L THIN QFN, 3x3x0.75mm                                           |                                 |

| APPROVAL                                                                                                | DOCUMENT CONTROL NO.<br>21-0136 |

| REV. O                                                                                                  | 2/2                             |

## Revision History

| REVISION NUMBER | REVISION DATE | DESCRIPTION                                                                                                            | PAGES CHANGED |

|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------|---------------|

| 0               | 9/13          | Initial release                                                                                                        | —             |

| 1               | 11/13         | Removed future product reference                                                                                       | 21            |

| 2               | 8/14          | Added THD+N TQFN typical only spec to <i>Electrical Characteristics</i> table                                          | 3             |

| 3               | 1/15          | Added <i>Table of Contents</i> , updated SSM spec, replaced all typical operating characteristics, and corrected typos | 5–12, 16–18   |

| 4               | 8/15          | Corrected package outline for WLP package                                                                              | 24            |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at [www.maximintegrated.com](http://www.maximintegrated.com).

*Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.*

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

[MAX98358EVL+T](#) [MAX98358ETE+T](#) [MAX98358ETE+](#) [MAX98358EVSYS#WLP](#) [MAX98358EVSYS#TQFN](#)